Cadence annuncia il processore Tensilica DNA 100 per applicazioni di AI

Cadence Design Systems ha annunciato l’IP del processore Tensilica DNA 100.

Si tratta di un’unità di elaborazione AI dotata di acceleratore di rete neurale (DNA) che offre prestazioni elevate e alta efficienza energetica su una gamma potenze di calcolo da 0,5 a centinaia di TeraMAC (TMAC).

Il processore DNA 100 è stato progettato per applicazioni di AI per esempio nei veicoli autonomi (AV), ADAS, prodotti di sorveglianza, robot, droni, soluzioni di realtà aumentata (AR)/realtà virtuale (VR), smartphone, piattaforme smart home e IoT.

DNA 100 integra anche un DSP Tensilica che lo rende in grado di adattarsi a qualsiasi nuovo layer di rete neurale attualmente non supportato dai motori hardware, offrendo inoltre l’estensibilità e la programmabilità di un core Tensilica Xtensa tramite le istruzioni TIE (Tensilica Instruction Extension).

Il processore DNA 100 è dotato di una piattaforma software AI completa. La compatibilità con l’ultima versione del Tensilica Neural Network Compiler consente il supporto di framework IA avanzati, tra cui Caffe, TensorFlow, TensorFlow Lite, e di un’ampia gamma di reti neurali.

Contenuti correlati

-

I DSP Tensilica di Cadence per l’audio di NXP

I DSP Tensilica HiFi 5 di Cadence sono diventati un componente chiave nell’ultima famiglia di DSP audio per autoveicoli di NXP Semiconductors, consentendo di implementare funzionalità audio avanzate per veicoli software-defined di nuova generazione. NXP ha infatti...

-

Cadence espande la licenza di Pfizer al software di molecular design

Cadence Molecular Sciences (OpenEye), una business unit di Cadence, ha annunciato che Pfizer ha firmato un accordo per estendere ed espandere l’accesso ai prodotti Cadence e ai kit di strumenti di programmazione per la progettazione molecolare avanzata....

-

Cadence semplifica la progettazione da nodo a nodo e la migrazione del layout

Cadence Design Systems ha reso disponibile un flusso certificato di migrazione di progetto da nodo a nodo basato sul nuovo ambiente Cadence Virtuoso Studio alimentato da AI generativa. Il flusso è compatibile con i nodi avanzati di...

-

Il supporto di Cadence allo standard TSMC 3Dblox

Cadence Design Systems ha annunciato dei nuovi flussi di progettazione, basati sulla piattaforma Integrity 3D-IC, destinati a supportare lo standard 3Dblox TSMC per il partizionamento della progettazione front-end 3D nei sistemi complessi. Grazie a questa collaborazione, i...

-

EMC: una questione di compatibilità

La simulazione a livello di campo elettromagnetico consente di valutare le prestazioni EMC di dispositivi, circuiti e sistemi direttamente in fase di progetto Leggi l’articolo completo su EO 500

-

TRACE32 supporta il trace off-chip di Xtensa

Lauterbach ha annunciato la disponibilità del supporto per il trace off-chip di Xtensa. TRACE32 ha supportato sin dall’inizio il protocollo di trace on-chip Xtensa (TRAX), ma il trace off-chip consente di avere tempi di registrazione molto più...

-

Cadence ottimizza il software per realizzare reti neurali a bassa potenza

Cadence Design Systems ha ottimizzato il software HiFi Cadence Tensilica per i digital signal processors (DSP). In questo modo potrà eseguire in modo efficiente TensorFlow Lite for Microcontrollers, facente parte della piattaforma open source end-to-end TensorFlow per...

-

I DSP di Cadence Design Systems

Presso lo stand di Cadence Design System a Embedded World 2020, l’azienda mostrerà i suoi DSP Tensilica e i tool per la progettazione e la verifica di applicazioni automotive ed embedded. In particolare i visitatori potranno vedere...

-

Cadence nominata “TSMC Partner of the Year”

Cadence Design Systems annuncia di avere ricevuto da TSMC, nell’ambito dell’Open Innovation Platform (OIP) Ecosystem Forum di quest’anno, quattro riconoscimenti come “Partner of the Year”. Cadence è stata premiata per lo sviluppo congiunto dell’infrastruttura di progettazione N6, per...

-

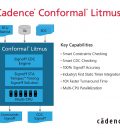

Cadence introduce il Conformal Litmus

Cadence Design Systems ha presentato Cadence Conformal Litmus, la soluzione di nuova generazione che offre funzioni di signoff per clock domain crossing (CDC) e constraints riducendo i tempi complessivi del ciclo di progettazione e migliorando la qualità del silicio...