Un futuro in 3D per i chip

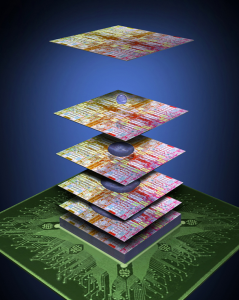

Per riuscire a incrementare ulteriormente la densità di integrazione dei microcircuiti, una delle soluzioni prospettate è quella di racchiudere più chip nel medesimo package, impilandoli uno sull’altro

Oggi, quando si parla di “3D”, si pensa subito ai nuovi film da vedere con gli appositi occhialini, oppure ai nuovi televisori già predisposti o ancora agli schermi dei pc più recenti. Nel settore microelettronico, invece, 3D significa ben altra cosa, e cioè la possibilità di sovrapporre direttamente più microchip, permettendo quindi di integrare nel medesimo contenitore più microcircuiti già singolarmente ottimizzati a livello di chip.

Al di là delle indubbie difficoltà che insorgono a livello realizzativo, comunque, i vantaggi sono consistenti. Il primo, ad esempio, è legato alla possibilità di ottenere una densità di integrazione finale più elevata di quella consentita dalla tecnologia dei singoli chip utilizzati, che sono spesso prossimi al loro limite tecnologico. Un secondo vantaggio è dato dalla possibilità di realizzare un dispositivo basato su tecnologie differenti, le quali spesso non sono disponibili nel medesimo chip o trovano la migliore implementazione in soluzioni di costruttori differenti: ciò permette infatti di utilizzare e affiancare prodotti standard singolarmente ottimizzati.

Un terzo vantaggio è dato dalla possibilità di ottenere elevate densità di integrazione in un’area ridotta, equivalente a quella dei singoli chip impilati, a tutto vantaggio della miniaturizzazione del prodotto finito.

Un quarto vantaggio può essere ottenuto grazie alla constatazione che le distanze che devono coprire i segnali per propagarsi lungo i bus di comunicazione sugli attuali chip (che ormai raggiungono dimensioni centimetriche) sono molto maggiori della distanza fra due chip sovrapposti, il che permette di ipotizzare il ricorso a comunicazioni “verticali” anziché orizzontali lungo il chip, potendo così rinunciare ai blocchi di amplificazione del segnale, ai repeaters, ai buffer di linea, e così via.

I segnali che collegano i vari chip sovrapposti viaggiano attraverso quelle che vengono chiamate le TSV, ovvero Through Silicon Vias, con struttura e funzioni del tutto analoghe alla omonime “via” comunemente utilizzate nei circuiti stampati di tipo multistrato. Ciò permette di ridurre il numero di blocchi funzionali richiesti, di ottenere migliori prestazioni e di ridurre la potenza assorbita.

Tutto ciò comporta ovviamente la riprogettazione del chip e del layout di alcuni circuiti, una diversa disposizione dei vari blocchi funzionali on-chip e la predisposizione di opportune unità di comunicazione inter-chip per massimizzare il throughput dei dati. Ne sono un chiaro esempio le maggiori prestazioni ottenute da alcune realizzazioni dimostrative quali processori, DSP e FPGA, le quali hanno potuto evidenziare prestazioni decisamente migliorate, parallelamente a consumi più contenuti.

Le tecnologie che a partire dall’inizio del nuovo millennio hanno sostanzialmente permesso di passare dalle tecnologie 2D a quelle 3D sono tre: la BGA (Ball Grid Array), la Flip-Chip e l’impiego dei package chip-scale.

Prestazioni superiori con il 3D

Poiché si tratta di soluzioni multi-chip, vengono alla memoria per similitudine le realizzazioni del tipo mcm o mcp (multi chip module e multi-chip package), oggi utilizzate ad esempio in molti azionamenti di potenza dove vi è la necessità di affiancare più chip con tecnologie differenti, dedicati all’elaborazione del segnale, alla trasmissione dati, alla traslazione dei segnali e al pilotaggio di potenza. Nelle realizzazioni di questo tipo, però, le esigenze sono differenti: innanzitutto manca la necessità di una miniaturizzazione spinta, e in secondo luogo occorre ben separare i vari chip sia per questioni termiche sia soprattutto per garantire un adeguato isolamento elettrico, condizionato ad esempio dal fatto di far coesistere chip di segnale con chip di potenza che operano a elevata tensione.

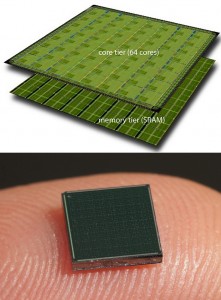

Varie sono state sino ad ora le realizzazioni basate su strutture tridimensionali, alcune delle quali presentate in conferenze e congressi. Alla ISSCC 2012, ad esempio, un team del Georgia Institute of Technology (in collaborazione con KAIST, Tezzaron, Amkor e Board Lab) ha presentato 3D-MAPS, ovvero il 3D MAssively Parallel processor with Stacked memory. La versione V1 è composta da 2 chip da 5 x 5 millimetri (Fig. 1), uno di elaborazione (integra 64 cpu) e uno di memoria Sram, mentre la versione V2 (da 10 x 10 millimetri) è composta da 5 chip sovrapposti, due di elaborazione (per un totale di 128 cpu) e tre di memoria Dram.

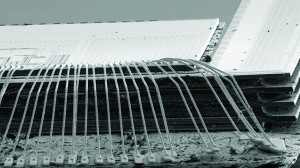

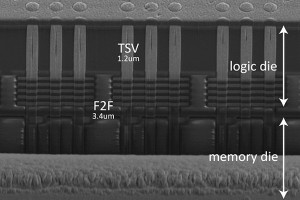

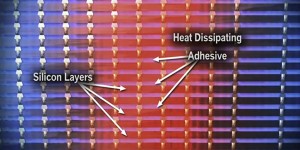

Fig. 2 – Sezione al microscopio elettronico del dispositivo dual-chip 3D-MAPS V1, in cui sono visibili le connessioni inter-chip tramite TSV; come si vede, i due chip sono face-to-face

La tecnologia TSV utilizzata (sezione di Fig. 2) è quella di Tezzaron, con via da 1.2 micrometri di diametro, mentre il chip è stato realizzato da GlobalFoundries in tecnologia da 130 nm e il packaging è di Amkor. Il processore integra 33 milioni di transistor, 50 mila interconnessioni TSV, per uno spessore totale di 0.8 millimetri. Il team ha utilizzato strumenti EDA standard 2D di Synopsys, Cadence e Mentor Graphics, realizzando poi degli appositi plug-ins per la gestione delle TSV e dei collegamenti 3D.

Rispetto ai processori standard, le prestazioni ottenute si sono dimostrate di assoluto rilievo. 3D-MAPS può infatti sfruttare un’ampiezza di banda per l’accesso alla memoria pari a 70.9 GB/sec, operando a 277 MHz x 64 (cpu) x 4 byte (1 word) dissipando meno di 5W. Al confronto, una cpu Intel i7 Extreme Edition abbinato a una Dram Samsung DDR3 da 1600 MHz offrirebbe una banda di 1600 MHz x 2 ch x 8 byte = 25.6 GB/s, e un Intel Xeon E7 abbinato a una DDR3 da 1066 MHz fornirebbe 1066 MHz x 4 ch x 8 byte = 34.1 GB/s; si tenga inoltre conto che sia l’i7 che lo Xeon E7 dissiperebbero una potenza decisamente più elevata.

Memorie in 3D

Nel panorama dei chip 3D, il settore che ha raggiunto per primo la maturità commerciale è indubbiamente quello delle memorie, dove la densità di impiccamento è essenziale per ottenere elevate capacità di memorizzazione. Varie sono infatti le società che da alcuni anni hanno prodotto soluzioni che vanno sotto il termine comprensivo di “stacked chip”. Sotto la spinta delle applicazioni consumer, infatti, sono state sviluppate soluzioni 3D per settori quali i dispositivi portatili (tablet, smartphone) o anche solo per la ormai onnipresenti usb-key.

Già nel 2007, ad esempio, Elpida aveva annunciato la realizzazione di una stacked-memory da addirittura 20 chip in soli 1.4 millimetri di spessore (Fig. 3). Per ottenere tale risultato, ciascun chip ha uno spessore di soli 30 micrometri, il che significa che occorre saper manipolare wafer spessi solo un trentesimo di millimetro!

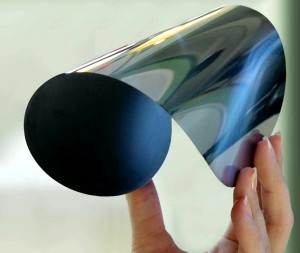

Fig. 4 – A spessori inferiori ai 50 micrometri i wafer diventano addirittura flessibili (foto PVA TePla)

Analogamente, si sono dovute mettere a punto tecniche di wire bonding anche per i collegamenti chip-to-chip, con lunghezze di soli 40 micrometri. Per raggiungere tali spessori, sono state sviluppate tecnologie in grado di operare su wafer ultrasottili, che a tali valori divengono addirittura flessibili, come si può vedere in figura 4. D’altronde, si è visto che i wafer con spessori inferiori ai 50 micrometri possono essere proficuamente sfruttati non solo per le soluzioni stacked-chip, ma anche per realizzare Igbt e Mosfet di potenza a bassa Rds(on).

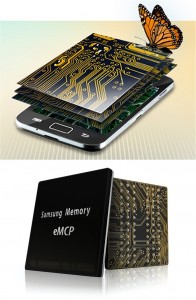

Fig. 5 – Samsung utilizza per i dispositivi di memoria ad alta densità una tecnologia Multi-Chip Package

Fra le società che utilizzano tecniche 3D vi è ad esempio Samsung, oggi leader nel settore dei circuiti per apparati mobili, che utilizza una tecnologia MCP (Multi-Chip Package, Fig. 5) per i propri dispositivi di memoria i quali, in una struttura stacked-chip, integrano memorie di vario tipo, combinando tecnologie di tipo Flash Nand SLC e Mmc con Mobile Dram quali LPDDR2 a 2 o 4 chip, come quelli utilizzati ad esempio negli ultimi iPad di Apple. I vantaggi ottenuti riguardano la minor potenza dissipata e la maggior velocità di accesso grazie all’intimo contatto fra i chip, il minor ingombro sul circuito stampato, il minor numero di componenti da inventariare e un più veloce time-to-market.

Toshiba, invece, ha scelto un approccio diverso, optando per la soluzione PoP, ovvero Package-on-Package.

Fig. 6 –Il concetto di “package-on-package” di Toshiba, una soluzione multi-chip per i dispositivi Asic e di memoria

Tale scelta permette il testing dei singoli package prima del bonding finale, e la sezione risultante è quella di figura 6, dalla quale si può vedere come in realtà Toshiba utilizza un package che integra due stacked-chip sovrapposto e connesso tramite array BGA a un supporto che ospita un terzo chip.

Anche Invensas (sussidiaria di Tessera) ha optato per soluzioni multi-chip per le proprie Dram, utilizzando un processo denominato xFD (ovvero multi-die face-down packaging) per incrementare drasticamente la densità di memoria e aumentare la velocità e l’efficienza dei chip di memoria, grazie ai collegamenti lunghi solo pochi micrometri.

Fig. 7 – Aspetto della soluzione utilizzata da Invensas per le proprie Dram multichip in tecnologia xFD

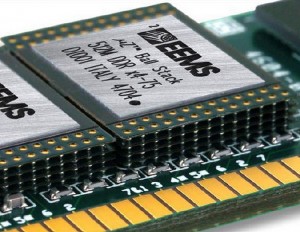

La medesima tendenza stanno seguendo non solo le Dram, ma anche le memorie Flash. Ne sono un esempio le recenti MicroSD Card da 32GB di SanDisk (visibili in Fig. 8), realizzate sovrapponendo 8 chip di memoria Flash in tecnologia da 32nm (Fig. 9) per uno spessore totale che – package plastico compreso – non supera il millimetro.

La medesima tendenza verso il 3D è evidenziata anche dall’ampia adesione al consorzio HMC, ovvero Hybrid Memory Cube, che raggruppa ormai decine di società. Fondato inizialmente da Samsung e Micron Technology, il consorzio HMC è gestito da una decina di sviluppatori, che provvedono a stabilirne le specifiche tecniche e di interfaccia. Fra i membri vi sono oggi Altera, ARM, HP, IBM, Intel, Open-Silicon, Hynix e Xilinx, e fra le società che hanno adottato lo standard figurano anche STMicroelectronics e Microsoft.

HMC rappresenta una soluzione innovativa nel panorama delle memorie Dram, in grado di offrire prestazioni avanzate in termini di velocità, consumi e costo.

Fig. 10 – Hybrid Memory Cube di IBM e Micron Technology rappresenta una realizzazione del tipo stacked-chip ad alta densità

I moduli HMC (Fig. 10) sono basati su una tecnologia di memoria ad alta velocità, applicata a pile di stacked-chip interconnessi tramite through-silicon-via (TSV) e connessi a un modulo di elaborazione logica e di controllo. I vantaggi offerti da questa tecnologia sono infatti in grado di offrire prestazioni pari a 15 volte quelle offerte da un tipico modulo DDR3, con un consumo per bit pari a solo al 70% di quello di una Dram DDR3 (Fig. 11).

Fig. 11 – I moduli HMC permettono significativi miglioramenti in termini di prestazioni e di consumi rispetto ai moduli Dram standard

Il risparmio di ingombro è altresì notevole, permettendo infatti una riduzione del 90% rispetto ai moduli RDIMM.

I primi moduli saranno disponibili nella seconda metà del 2013 in versioni da 2 GByte, utilizzeranno chip di Dram da 4 Gbit e garantiranno una velocità di I/O di 160 GByte/s, con una potenza dell’80% inferiore ai moduli DDR3 e DDR4. Non solo, ma l’accoppiata fra il substrato di elaborazione logica e lo stack di Dram permetterà una riduzione nel pin-count, che passerà dai 600 pin di una soluzione DDR3 a 4 canali a soli 65 pin di un modulo HMC.

Il trend

Per quanto riguarda la direzione a cui puntano queste nuove realizzazioni, è necessario guardare ai lavori più recenti dei vari laboratori impegnati in queste ricerche. È comunque indubbio che, nonostante le notevoli difficoltà realizzative, si è visto che i vantaggi che se ne possono ricavare sono in grado di giustificare gli investimenti soprattutto per i mercati di punta (a elevato valore aggiunto) e per i settori a più rapida espansione e caratterizzati da volumi molto elevati, come sono oggi quelli dei dispositivi mobili e dell’audio-video.

Persino nel settore degli Fpga si stanno attuando tecniche di chip-stacking, come dimostrano alcune pubblicazioni di Xilinx. La società, ad esempio, nella propria serie Virtex7 2000T integra quattro chip con oltre 10 mila connessioni inter-chip, il tutto ospitato in package da 45×45 millimetri, con ben 2025 pin.

Per quanto riguarda i processori, si ipotizza che nei prossimi anni saranno disponibili dispositivi che integrano decine o addirittura centinaia di cpu. Tali processori, per operare adeguatamente, richiederanno necessariamente un’enorme ampiezza di banda di memoria, che potrà essere garantita solo aumentando il parallelismo delle connessioni con la cpu. Ciò significa dover ricorrere a un elevato numero di bump e/o di TSV.

Con l’aumentare del numero di chip impilati, al di là dei problemi realizzativi e di affidabilità delle interconnessioni, uno dei problemi associato alle realizzazioni ad alta densità è rappresentato dal calore prodotto, che in queste realizzazioni può essere smaltito in maniera sensibilmente più difficoltosa rispetto al singolo chip ospitato in un package adeguato. Le soluzioni non sono semplici: si parla di utilizzare elementi di separazione fra i chip realizzati in ceramica, oppure di utilizzare liquidi refrigeranti interni al package (come ipotizzato ad esempio nell’ambito del progetto ICECool del DARPA statunitense), oppure ancora l’impiego di substrati metallici.

Fig. 12 – Grazie a una particolare colla sviluppata da 3M, IBM ha realizzato un array di processori composto da oltre 100 chip impilati

La dissipazione del calore può non essere un problema per un numero ridotto di chip, ma quando si utilizza una “pila” composta da un elevato numero di singoli componenti, allora il problema termico diviene assolutamente condizionante. Già un anno fa IBM aveva annunciato di aver realizzato un processore a elevate prestazioni ottenuto impilando oltre 100 chip (Fig. 12), utilizzando una particolare colla con riempimento ceramico a elevata conduttività termica sviluppata da 3M.

Ogni chip possiede un pin-grid array nella parte inferiore e un array ball-grid nella parte superiore, e i singoli processori sono connessi in serie (Fig. 13). Secondo le previsioni, i primi prodotti di questo tipo dovrebbero essere disponibili nel corso del 2013.

Fig. 13 – Nella realizzazione multi-chip di IBM, i singoli processori sono interconnessi alternativamente tramite array di pin-grid e di ball-grid

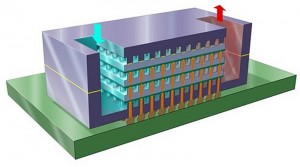

Un’altra tecnica sperimentata dai laboratori di ricerca di Zurigo della stessa IBM per un efficace raffreddamento degli array multichip è quella a circolazione forzata di acqua (Fig. 14), una soluzione messa a punto in collaborazione con il Fraunhofer Institute. Infatti, realizzando dei microcanali da 50 micrometri all’interno dello strato isolante interposto fra i chip, la società è riuscita a ottenere una dissipazione pari a 180 watt/cm2 per ciascun strato, con un footprint totale di 4 cm2.

Fig. 14 – Una delle soluzioni per il raffreddamento degli array multichip sperimentata da IBM è costituita dalla circolazione di acqua attraverso microcanali

L’intero blocco logico – composto da molti strati – riesce così a dissipare oltre 1 kilowatt di potenza. Per garantire un adeguato isolamento elettrico dei chip nonostante la circolazione di acqua, è stato necessario incapsulare completamente i vari chip con un opportuno collante, isolando ermeticamente anche le interconnessioni fra i vari chip sovrapposti.

Le previsioni

Secondo le previsioni contenute nella pubblicazione “3D IC and TSV Interconnect Market” di MarketsandMarkets, il mercato globale dei circuiti integrati 3D dovrebbe crescere dai 2.21 B$ del 2009 ai 6.65 B$ del 2016, con un Cagr del 16,9% dal 2011 al 2016. Secondo il medesimo report, i prodotti maggiormente interessati dalla transizione 2D-3D saranno le memorie e i sensori (ad esempio quelli d’immagine Cmos), mentre il mercato trainante sarà soprattutto quello consumer, con prodotti di punta quali memorie ibride, processori grafici e circuiti per le comunicazioni wireless.

Paolo De Vittor

Contenuti correlati

-

Inova Semiconductors riceve il premio Digital Innovator 2023

Inova Semiconductors è stata nominata “Digital Innovator” per il terzo anno consecutivo dalla rivista di PC Chip insieme agli esperti di Globis Management Consulting. Chip ha condotto un’indagine sulle innovazioni digitali con l’obiettivo di trovare aziende tedesche...

-

I chip chiave per Industria 4.0

Alcune categorie di circuiti integrati stanno guidando la crescita dei chip dedicati al mondo della Internet of Things. In uno studio sul comparto, la società di ricerca IoT Analytics individua quattro categorie principali: MCU, chip di connettività,...

-

Identificazione ottica ed elaborazione delle immagini

Tutto ciò che ci circonda e che possiamo percepire non è altro che un segnale variabile nel tempo: la sensazione tattile del caldo, il gusto dolce o amaro, il suono proveniente da un altoparlante, sono tutti segnali...

-

Vicor apre il primo impianto di produzione “ChiP”

Vicor ha inaugurato il suo nuovo impianto per la produzione di moduli di potenza. Si tratta del primo impianto di fabbricazione ChiP (Converter housed in Package) e consente una produzione di moduli di alimentazione più scalabile, automatizzata...

-

TouchNetix presenta la nuova generazione di interfacce utente 3D touchless

TouchNetix ha annunciato i chip touchscreen aXiom che offrono nuove capacità di rilevamento 3D rilevando i gesti e consentendo funzioni touchless per una varietà di ambienti automotive, industriali e consumer. aXiom fornisce un rapporto segnale/rumore (SNR) oltre...

-

Intel potrebbe realizzare una fabbrica di chip in Italia

Secondo alcune indiscrezioni provenienti da tre fonti contattate da Reuters, Intel potrebbe aprire una fabbrica di semiconduttori in Italia. Gli esperti, del resto, sottolineano che Pat Gelsinger, CEO di Intel, aveva già fatto dichiarazioni in merito a...

-

Infineon apre una nuova fabbrica di chip per l’elettronica di potenza in Austria

Infineon Technologies ha aperto ufficialmente la sua nuova fabbrica di chip per l’elettronica di potenza su wafer sottili da 300 millimetri a Villach, in Austria. Con il motto “Ready for Mission Future“, il CEO di Infineon Reinhard...

-

Disponibile da Farnell il chip RP2040 di Raspberry Pi

Farnell ha annunciato la disponibilità del chip RP2040 e quindi il chip progettato da Raspberry Pi e parte fondamentale della scheda di sviluppo Raspberry Pi Pico, è ora disponibile come componente indipendente. RP2040 dispone di due core...

-

Il primo chip a 2 nm di IBM

IBM ha annunciato lo sviluppo del primo chip basato sulla sua tecnologia a 2 nanometri (nm) nanosheet. La tecnologia è stata sviluppata nel laboratorio di ricerca situato presso l’Albany Nanotech Complex di Albany, NY, dove gli scienziati...

-

Volkswagen svilupperà i chip per le sue auto

Una notizia particolarmente interessante per il mondo automotive e per quello dell’elettronica è che Volkswagen intende progettare e sviluppare internamente i suoi chip ad alte prestazioni e il software per i veicoli a guida autonoma. A dichiararlo...