Logiche programmabili più eterogenee grazie ai nuovi FinFET da 16 nm

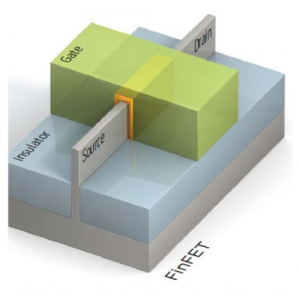

Fig. 1 – Rispetto ai transistor in geometria di riga da 20 nm i FinFET con larghezza del canale di 16 nm fabbricati da TSMC hanno il 40% in più di velocità e consumano il 60% in meno

Protagonisti dell’ultima generazione degli Fpga Xilinx sono i transistor FinFET nei quali il canale di conduzione che collega emettitore e collettore attraversa sopra-die la base uscendone fuori ai due lati formando due “pinne” (fin). La forma un po’ più verticale di questi transistor rispetto ai transistor più tradizionalmente planari ne ha favorito la denominazione di 3D ma non c’è dubbio che questo approccio riduca resistenza di conduzione e capacità parassita nella zona del canale circondata dalla base e perciò migliora l’efficienza delle commutazioni.

Nelle fonderie taiwanesi TSMC sono stati accesi quest’anno gli impianti produttivi per la fabbricazione dei circuiti in geometria di riga da 16 nm disegnati con i transistor 16FF+ FinFET 3D e grazie a ciò Xilinx ha iniziato la produzione dei nuovi Fpga UltraScale+. Il passo avanti nei transistor è stato possibile grazie al miglioramento del processo di deposizione della base con la litografia a 193 nm e i nuovi transistor evidenziano così una velocità superiore del 40% rispetto ai transistor in geometria di riga da 20 nm e del 65% rispetto a quelli da 28 nm mentre il consumo di potenza scende rispettivamente del 60% e del 70%.

L’architettura UltraScale è stata sviluppata dai ricercatori Xilinx per superare la limitatezza delle interconnessioni fra i moduli dentro i chip multicore e grazie a ciò scalare dalla geometria di riga da 20 nm a 16 nm. Per permettere ai transistor di commutare più velocemente e a ciascun blocco funzionale di eseguire più rapidamente le task multiple, infatti, occorre migliorare il trasferimento dei segnali nel chip, la distribuzione del clock e i flussi di simboli attraverso le interconnessioni.

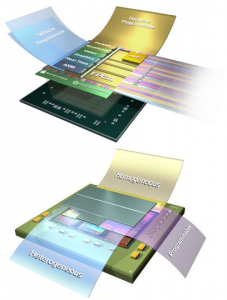

Fig. 2 – L’architettura UltraScale+ è definita da Xilinx “3D-on-3D” perché consente di implementare nei chip più moduli differenziabili nelle prestazioni e nella gestione delle interconnessioni

La tecnologia di ottimizzazione delle connessioni SmartConnect permette di ottenere la velocità operativa dell’ordine dei teraflops necessaria per gli Fpga di nuova generazione e l’architettura UltraScale è stata concepita proprio a tal scopo. Innanzitutto offre la possibilità di implementare la distribuzione multi-zona dei dati, del clock e persino dell’alimentazione e ciò consente di ottimizzare l’instradamento dei segnali eliminando i colli di bottiglia nei percorsi critici e ottenere velocità nei bus di più terabit al secondo. Inoltre, aumenta le risorse a bordo in termini di memoria e di I/O e pertanto migliorano le prestazioni dei chip composti da numerosi core singoli.

3D-on-3D

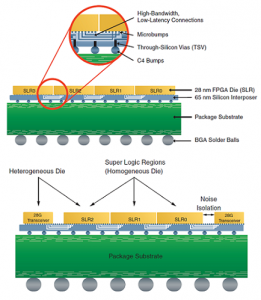

Xilinx definisce i suoi nuovi UltraScale+ dei Multi-Processing SoC (MPSoC) 3D-on-3D perché, innanzi tutto, sono fatti con più moduli circuitali disegnati con transistor FinFET 3D e poi perché hanno un grado di libertà in più rispetto ai consueti SoC perché possono essere differenziati dal punto di vista funzionale. Tutti i moduli si appoggiano su un unico strato intermedio di 65 nm dove grazie alla Stacked Silicon Interconnect Technology (SSI) condividono le connessioni interne ad alta velocità sia fra gli elementi funzionali omogenei sia fra i core di bordo con funzionalità specifiche come le GPU o le memorie e, inoltre, per i moduli più esigenti hanno anche la possibilità di appoggiarsi ai transceiver interni ad altissima velocità (28 Gbps).

Fig. 3 – Gli Fpga Xilinx UltraScale+ ospitano moduli omogenei come gli array di porte logiche insieme a moduli specifici come core CPU, GPU, memorie UltraRam e interfacce ad alta velocità PCIe Gen4 e 100G Ethernet

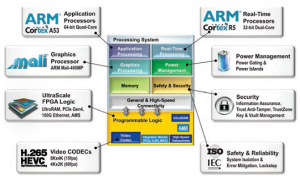

Lo strato intermedio si appoggia poi a un vero e proprio substrato che ne permette il montaggio sullo zoccolo della scheda. La novità è che i moduli possono essere scelti tutti uguali laddove devono funzionare come array di porte logiche ma possono anche essere molto diversi fra loro se occorre che svolgano mansioni ben definite o custom. Questo approccio permette di assegnare mansioni differenti alle diverse zone del chip ma consente anche di programmare e riconfigurare ciascun modulo e dunque offre la massima versatilità da entrambi i punti di vista hardware e software. Nei nuovi Fpga UltraScale+ possiamo trovare, per esempio, da uno a quattro core ARM Cortex A53, un processore grafico ARM Mali-400, un abbondante blocco di memoria UltraRAM, un modulo video codec H.265 e le interfacce DisplayPort, PCIe Gen4 e 100G Ethernet, oltre a un’indispensabile Power Management Unit.

Questa eterogeneità dei moduli operativi è frutto del perfezionamento della tecnologia Zynq UltraScale+ MPSoC che consente di scegliere “the right engines for the right tasks” e personalizzare ogni dispositivo su misura per l’applicazione alla quale è destinato.

Fig. 4 – Grazie ai FinFET da 16 nm gli Fpga diventano eterogenei e personalizzabili con la dotazione hardware e la programmazione software su misura per ogni applicazione

Oltre a rendere gli Fpga ancor più competitivi rispetto agli Asic, la geometria di riga di 16 nm permette di disegnare memorie UltraRAM a bordo con capienza fino a 432 Mbit e di questo vantaggio ne beneficiano tutti i moduli installati con un miglioramento del rapporto prestazioni/watt osservato nei test da due a cinque volte maggiore rispetto agli analoghi dispositivi in geometria di riga da 28 nm. Xilinx e TSMC stanno procedendo di gran passo con lo sviluppo dei processi di fabbricazione in geometria di riga da 10 nm e da 7 nm che potrebbero essere annunciati nel 2017 ma il condizionale è d’obbligo perché le dimensioni del canale impongono difficoltà quantistiche per le quali è probabile che ci vorrà un po’ di tempo.

Lucio Pellizzari

Contenuti correlati

-

ROHM e TSMC collaborano per lo sviluppo della tecnologia GaN per l’automotive

La nuova partnership strategica tra ROHM e TSMC è focalizzata sullo sviluppo e la produzione in serie di dispositivi di potenza al nitruro di gallio (GaN) destinati ad applicazioni per veicoli elettrici. Il contributo di ROHM sarà...

-

Tecnologia CoWoS di TSMC per il nuovo sottosistema di Alphawave Semi

Alphawave Semi ha annunciato la disponibilità del primo sottosistema Die-to-Die (D2D) Universal Chiplet Interconnect Express (UCIe) a 3 nm basato sulla tecnologia di packaging avanzata Chip-on-Wafer-on-Substrate (CoWoS) di TSMC. Questo sottosistema, sviluppato in stretta collaborazione con TSMC,...

-

Microchip Technology amplia la partnership con TSMC

Microchip Technology ha annunciato di aver ampliato la sua partnership con TSMC per abilitare una capacità produttiva specializzata a 40 nm presso la sua sussidiaria JASM, nella prefettura di Kumamoto in Giappone. Questa partnership fa parte della...

-

Uno sguardo all’evoluzione delle Flash NOR

Le memorie Flash NOR esterne da 1,2 V di ultima generazione assicurano un maggiore risparmio energetico nei prodotti basati su SoC realizzati con geometrie inferiori a 10 nm Leggi l’articolo completo su EO 515

-

Cadence amplia il portafoglio IP per il processo TSMC N3E

Cadence Design Systems ha ampliato la sua offerta di IP di progettazione estendendola al processo a 3 nm di TSMC (N3E). Queste soluzioni mettono a disposizione dei clienti un’ampia gamma di IP di memoria e interfacce ad...

-

Socionext annuncia la collaborazione con Arm e TSMC

Socionext ha annunciato una collaborazione con Arm e TSMC per lo sviluppo di un innovativo chiplet con CPU a 32 core ottimizzato dal punto di vista energetico e realizzato con la tecnologia da 2 nm di TSMC....

-

Virtuoso Studio Cadence supporta i flussi di riferimento RF e mmWave per i processi di TSMC

Cadence Design Systems ha collaborato con TSMC per integrare la nuova versione di Virtuoso Studio nei flussi di riferimento N16 mmWave e N6RF di TSMC. La società ha anche annunciato il supporto aggiuntivo per il flusso di...

-

Riconoscimento alla Innovation Zone europea di TSMC per gli HEMT ICeGaN di CGD

Il SoC HEMT GaN ICeGaN di Cambridge GaN Devices (CGD) ha ottenuto il riconoscimento “Miglior demo” alla Innovation Zone del 2023 Europe Technology Symposium di TSMC. CGD evidenzia che il suo ICeGaN , che è ora nella...

-

Gli acceleratori hardware

L’implementazione di acceleratori è ormai imprescindibile per molte applicazioni e i vantaggi di queste soluzioni sono indispensabili non soltanto per migliorare le prestazioni ma anche per ridurre i consumi e i costi Leggi l’articolo completo su EO...

-

Cadence e TSMC collaborano per accelerare l’innovazione delle applicazioni radar, 5G e wireless

Cadence Design Systems ha collaborato con TSMC per l’ottimizzazione della piattaforma Cadence Virtuoso per il flusso di riferimento di progettazione mmWave a 79 GHz su processo N16 di TSMC. Grazie a questo sviluppo, i clienti comuni hanno...