Le piattaforme Mentor Calibre e Analog FastSPICE ottengono la certificazione per i più recenti processi di TSMC

Mentor ha annunciato di aver ottenuto la certificazione per un’ampia gamma di tool di progettazione di circuiti integrati per le tecnologie di processo N5 e N6 di TSMC. Inoltre, la collaborazione di Mentor con TSMC si è estesa alla tecnologia di packaging avanzata, sfruttando ulteriormente la tecnologia 3DSTACK della piattaforma Calibre di Mentor per supportare le piattaforme di packaging avanzate di TSMC.

Le tecnologie di processo N5 e N6 di TSMC aiutano molte delle principali società di progettazione di IC del mondo a migliorare le prestazioni, ridurre i fattori di forma e ridurre il consumo di energia per i processori destinati a mercati altamente competitivi come quello automotive, Internet of Things, elaborazione ad alte prestazioni, mobile/infrastrutture 5G, intelligenza artificiale e altri.

“La lunga e fruttuosa collaborazione di Mentor con TSMC continua ad aiutare i nostri clienti comuni a fornire circuiti integrati altamente innovativi e differenziati”, ha affermato Joe Sawicki, executive vice president del segmento IC di Mentor. “Mentor è lieta di estendere questa collaborazione con le recenti certificazioni delle piattaforme di progettazione Mentor per le più recenti e avanzate tecnologie di processo per semiconduttori di TSMC. ”

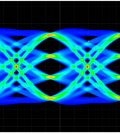

Tra le numerose tecnologie di progettazione di Mentor recentemente certificate per i processi N5 e N6 di TSMC ci sono quella Calibre nmPlatform per la verifica fisica degli IC, il tool Calibre xACT e la piattaforma Analog FastSPICE (AFS) per la verifica di circuiti di circuiti digitali analogici custom, memorie, circuiti per radio frequenza (RF) e mixed signal.

Oltre a queste certificazioni, Mentor ha anche annunciato che la sua piattaforma AFS ora supporta le piattaforme di progettazione mobile e ad alte prestazioni (HPC) di TSMC.

La certificazione consente ai clienti di Mentor che si rivolgono a progetti analogici, a segnale misto e radiofrequenza per le applicazioni HPC di verificare i propri chip per i più recenti processi TSMC.

Mentor ha anche annunciato una collaborazione con TSMC per sfruttare ulteriormente gli strumenti di packaging 3DSTACK di Calibre per supportare la tecnologia di packaging CoWoS di TSMC.

Contenuti correlati

-

ROHM e TSMC collaborano per lo sviluppo della tecnologia GaN per l’automotive

La nuova partnership strategica tra ROHM e TSMC è focalizzata sullo sviluppo e la produzione in serie di dispositivi di potenza al nitruro di gallio (GaN) destinati ad applicazioni per veicoli elettrici. Il contributo di ROHM sarà...

-

Tecnologia CoWoS di TSMC per il nuovo sottosistema di Alphawave Semi

Alphawave Semi ha annunciato la disponibilità del primo sottosistema Die-to-Die (D2D) Universal Chiplet Interconnect Express (UCIe) a 3 nm basato sulla tecnologia di packaging avanzata Chip-on-Wafer-on-Substrate (CoWoS) di TSMC. Questo sottosistema, sviluppato in stretta collaborazione con TSMC,...

-

Microchip Technology amplia la partnership con TSMC

Microchip Technology ha annunciato di aver ampliato la sua partnership con TSMC per abilitare una capacità produttiva specializzata a 40 nm presso la sua sussidiaria JASM, nella prefettura di Kumamoto in Giappone. Questa partnership fa parte della...

-

Uno sguardo all’evoluzione delle Flash NOR

Le memorie Flash NOR esterne da 1,2 V di ultima generazione assicurano un maggiore risparmio energetico nei prodotti basati su SoC realizzati con geometrie inferiori a 10 nm Leggi l’articolo completo su EO 515

-

Cadence amplia il portafoglio IP per il processo TSMC N3E

Cadence Design Systems ha ampliato la sua offerta di IP di progettazione estendendola al processo a 3 nm di TSMC (N3E). Queste soluzioni mettono a disposizione dei clienti un’ampia gamma di IP di memoria e interfacce ad...

-

Socionext annuncia la collaborazione con Arm e TSMC

Socionext ha annunciato una collaborazione con Arm e TSMC per lo sviluppo di un innovativo chiplet con CPU a 32 core ottimizzato dal punto di vista energetico e realizzato con la tecnologia da 2 nm di TSMC....

-

Virtuoso Studio Cadence supporta i flussi di riferimento RF e mmWave per i processi di TSMC

Cadence Design Systems ha collaborato con TSMC per integrare la nuova versione di Virtuoso Studio nei flussi di riferimento N16 mmWave e N6RF di TSMC. La società ha anche annunciato il supporto aggiuntivo per il flusso di...

-

Riconoscimento alla Innovation Zone europea di TSMC per gli HEMT ICeGaN di CGD

Il SoC HEMT GaN ICeGaN di Cambridge GaN Devices (CGD) ha ottenuto il riconoscimento “Miglior demo” alla Innovation Zone del 2023 Europe Technology Symposium di TSMC. CGD evidenzia che il suo ICeGaN , che è ora nella...

-

Gli acceleratori hardware

L’implementazione di acceleratori è ormai imprescindibile per molte applicazioni e i vantaggi di queste soluzioni sono indispensabili non soltanto per migliorare le prestazioni ma anche per ridurre i consumi e i costi Leggi l’articolo completo su EO...

-

Cadence e TSMC collaborano per accelerare l’innovazione delle applicazioni radar, 5G e wireless

Cadence Design Systems ha collaborato con TSMC per l’ottimizzazione della piattaforma Cadence Virtuoso per il flusso di riferimento di progettazione mmWave a 79 GHz su processo N16 di TSMC. Grazie a questo sviluppo, i clienti comuni hanno...