26

- ELETTRONICA OGGI 443 - MARZO 2015

TECH INSIGHT

ELETTRONICA 3D

interna delle celle standard

permetterà di affrontare in

maniera più efficace alcuni

dei problemi imputabili alla

migrazione verso processi

nanometrici basati sui fin-

FET. Nel momento in cui i

progettisti cercheranno di

trarre vantaggi dalle mag-

giori prestazioni offerte dai

transistor 3D e dall’aumento

delle velocità di clock, do-

vranno affrontare proble-

matiche sempre più com-

plesse legate alla variabilità.

Sebbene i transistor finFET

siano caratterizzati da mino-

ri variazioni rispetto ai tran-

sistor planari relativamente

ad alcuni parametri chiave,

la variabilità rappresenta

il maggior ostacolo per il

signoff (ovvero la verifi-

ca) delle temporizzazioni e

compare in un certo numero

di modalità che interessano

sia le celle standard sia lo

strato di sbroglio.

Tradizionalmente tali va-

riazioni saranno incorpo-

rate all’interno di bande di

guardia (guard band) che

limitano la velocità di clock,

penalizzando in tal modo i

vantaggi in termini di pre-

stazioni ottenibili con una

struttura finFET. Analisi più

approfondite e tecniche di

correzione adeguate per-

mettono di limitare sen-

sibilmente tali perdite di

prestazioni, garantendo ve-

locità di clock più elevate e

permettendo l’introduzione

sul mercato di prodotti più

competitivi. Le tecniche di

double patterning adottate

nei processi basati su fin-

FET con geometrie da 14 e

16 mm hanno evidenziato

variazioni significative nei

ritardi di percorso (path de-

lay). Per esempio un piccolo

spostamento

nell’allinea-

mento di una delle due ma-

schere utilizzate per trasfe-

rire l’immagine dei pattern

di interconnessione può

portare a un aumento della

capacità di accoppiamen-

to tra l’elettrodo del gate

e l’insieme dei conduttori,

con conseguente incremen-

to del ritardo di percorso.

Poiché questo spostamento

sarà coerente per l’intera

maschera, il ritardo per i

transistor collegati dal pat-

tern su quella maschera

saranno correlati; questo

fattore deve essere preso in

considerazione dai tool di

analisi più avanzati capaci

di “comprendere” il com-

portamento e i collegamen-

ti interni di ciascuna cella

standard. Prendendo in

considerazione queste cor-

relazioni e adottando misure

correttive adeguate, è possi-

bile eliminare gli effetti im-

putabili alla variazioni della

capacità di accoppiamento

e incrementare le velocità

di clock. Gli effetti parassi-

ti dell’interconnessione, in

particolar modo l’elevata

resistenza delle piste di me-

tallo presenti nei processi

basati sulla tecnologia fin-

FET, limitano le prestazioni

della rete di distribuzione

del clock (clock tree), che

utilizza un gran numero di

connessioni su lunga di-

stanza per fornire una tem-

porizzazione coerente per

tutto il circuito integrato.

Le tecniche tradizionali che

prevedono l’adozione di un

buffer comportano un in-

cremento del consumo di

potenza. Una miglior cono-

scenza delle celle standard

permette di effettuare un’ot-

timizzazione più “intelligen-

te” della rete di distribuzione

del clock e di fornire segnali

di temporizzazione a bas-

so skew senza penalizzare

il budget di potenza. La di-

minuzione della geometria

dei dispositivi comporta un

incremento della probabili-

tà che si verifichino eventi

di tipo SEU (SingleEvent

Upset) prodotti da radiazio-

ni ionizzanti che possono

causare risultati non corret-

ti o malfunzionamenti del si-

stema. L’analisi della struttu-

ra delle celle all’interno del

circuito e la loro sostituzio-

ne con version “hardened”

(ovvero resistenti alle radia-

zioni) permettono di ridurre

la probabilità di comporta-

menti non corretti in presen-

za di particelle alfa.

Il passaggio a processi ba-

sati su finFET

è associato

un certo numero di variazio-

ni a livello di processo che

hanno implicazioni sul pro-

getto digitale; se non tenute

nella giusta considerazione,

esse possono penalizzare le

prestazioni del circuito inte-

grato. Sebbene questi effetti

fisici potrebbero costituire

una “minaccia” per un flusso

di progetto ampiamente col-

laudato come quello basato

su celle standard, l’introdu-

zione di tool espressamente

ideati per il progetto di SoC

a livello di cella assicura-

no la stabilità di tale flusso,

permettendo nel contempo

di sfruttare al meglio le pre-

stazioni dei processi basati

sui finFET.

Q

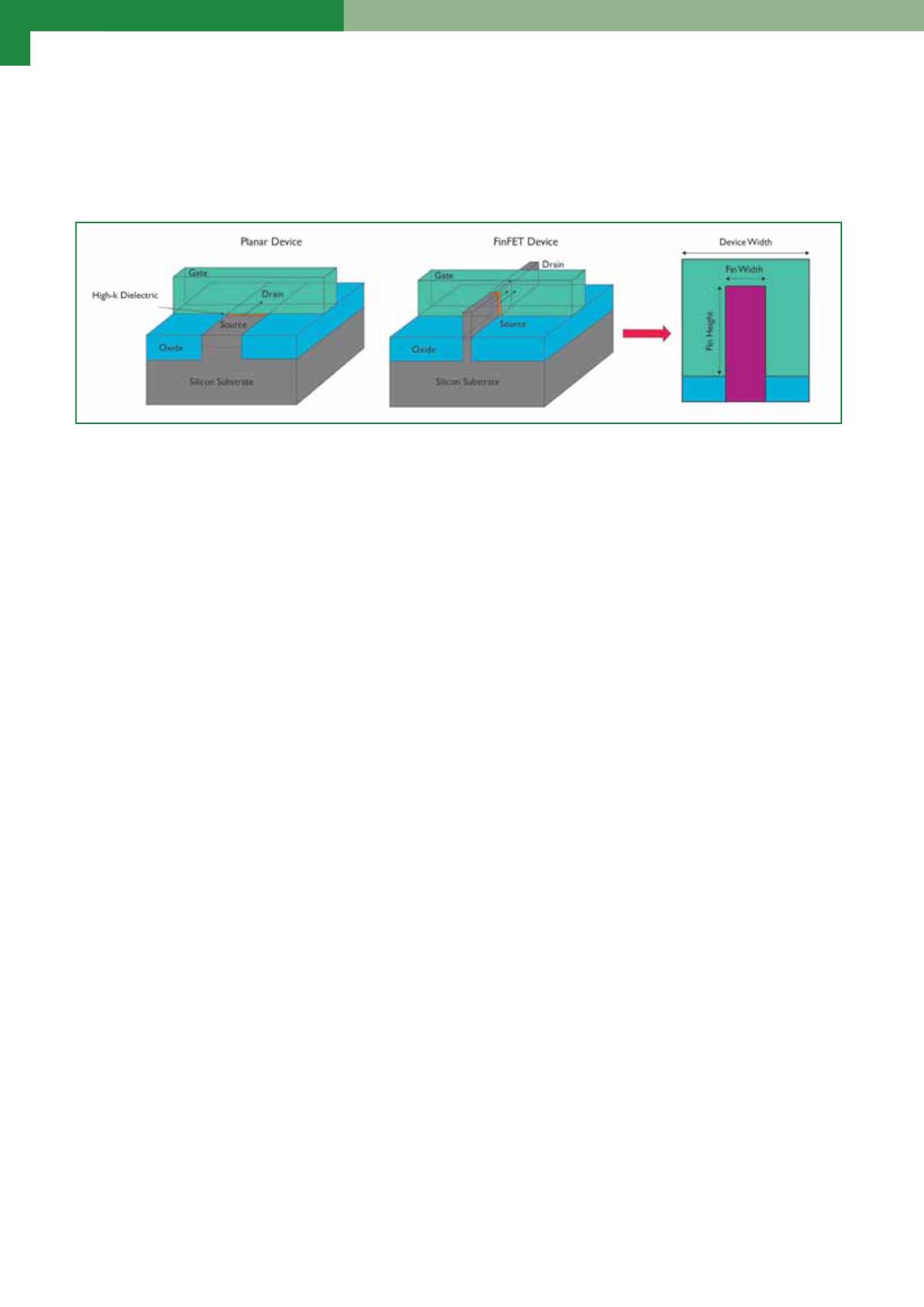

Fig. 2 – Confronto tra un transistor finFET e un transistor planare