25

- ELETTRONICA OGGI 443 - MARZO 2015

TECH INSIGHT

ELETTRONICA 3D

Il processo impiegato per

realizzare le alette sfrutta tec-

niche di auto-allineamento

chimico, grazie alle quali è

possibile ottenere un passo

inferiore del 25% rispetto

al passo delle linee relati-

ve agli strati più sottili di

un’interconnessione metal-

lica, M1 e M2. Questi strati

di metallo sono attualmen-

te tracciati utilizzando due

maschere indipendenti, che

sono sovrapposte mediante

un processo di esposizio-

ne composito piuttosto che

tramite processi di auto-al-

lineamento. Il passo minimo

di questi strati di metallo è

determinato dall’errore di so-

vrapposizione, che dà come

risultato un passo maggiore

rispetto a quello ottenibile

con il processo di auto-alli-

neamento impiegato per la

formazione dell’aletta. La di-

vergenza tra il passo dell’in-

terconnessione metallica M2

– che convenzionalmente

scorre parallela all’aletta – e

dell’aletta stessa deve essere

tenuta in considerazione nel

progetto delle celle standard

utilizzate per implementare il

substrato (bulk) della logica

digitale che sarà utilizzata in

un circuito integrato basato

su finFET.

Nel caso dei processi ba-

sati sulla tecnologia finFET,

vi sono solamente alcune

combinazioni possibili tra

passi dell’interconnessione

metallica e delle alette che

possano dar vita a librerie

di celle standard utilizzabili,

che devono essere realizzate

in modo da far corrisponde-

re ciascuna delle loro celle

a un numero fisso di piste.

Anche in questo caso alcune

combinazioni daranno vita a

griglie di metallo non modifi-

cabili che rendono difficile il

trasporto di una quantità di

corrente sufficiente alle celle

sui percorsi critici. I proces-

si nanometrici sono sensibili

in misura sempre maggiore

a effetti quali l’elettro-migra-

zione, che riduce la vita ope-

rativa di un circuito integrato

assottigliando gradualmente

i conduttori soggetti a cor-

renti di elevata intensità fino

al momento in cui essi si

rompono.

Tool più “intelligenti”

Per ottimizzare la densità del-

le connessioni metalliche, le

regole del double-patterning

(tecnica che prevede l’uso di

due esposizioni successive

per ottenere il pattern interno

di un singolo strato) impon-

gono non solo il passo delle

piste di metallo ma anche la

loro ampiezza. Quindi non è

sempre possibile tracciare

piste di metallo più ampie

per il trasporto delle correnti

di maggiore intensità neces-

sarie per le celle che devono

garantire un’elevata capacità

di pilotaggio. Alcune combi-

nazioni tra numero di alette

e numero di piste di metallo

consentono un uso più fles-

sibile dell’interconnessione

di metallo per l’istradamen-

to dei segnali di potenza.

In questo modo è possibile

utilizzare terminali (rail) di

potenza più ampi e più resi-

lienti laddove sono richiesti,

unitamente a piste di celle in

grado di garantire il miglior

compromesso tra maggiore

densità di routing logico e

potenza erogata.

Per sfruttare in modo ade-

guato queste strutture, è ne-

cessaria una conoscenza più

approfondita dell’architettura

della cella standard rispetto

a quella richiesta quando si

utilizzano i tradizionali tool di

piazzamento e sbroglio (pla-

ce & route), che sono proget-

tati in modo tale che le celle

standard possano essere

considerate delle semplici

“scatole nere” dotate di un

insieme di pin di I/O e di po-

tenza, situate in posizioni ben

definite.

I tool che sono in grado di

utilizzare la conoscenza

dell’architettura interna delle

celle standard e di rimappare

le celle in funzione dei requi-

siti della logica possono ga-

rantire la flessibilità richiesta

per sfruttare al meglio queste

nuove strutture, senza richie-

dere un completo re-tooling

del flusso di implementa-

zione di un circuito integra-

to. Questa conoscenza può

essere utile in altre fasi del

flusso di progetto, fino alle

ultime modifiche di progetto

che danno origine all’ECO

(Engineering Change Order –

ovvero le modifiche effettua-

te una volta che il prodotto è

pronto per la produzione).

Poich

é

le regole di progetto

sono più severe rispetto al

passato, l’implementazione di

un’operazione di ECO risul-

ta più difficile perché anche

solo una piccola variazione

può portare all’insorgere di

problemi con la colorazio-

ne della maschera su strati

che utilizzano la tecnica del

double-patterning. Un flus-

so che integra tool capaci di

“comprendere” l’ambiente lo-

cale delle celle standard può

manipolare il progetto più in

profondità, per consentire

l’implementazione dell’ECO

nella maniera più trasparente

possibile. Una migliore com-

prensione dell’architettura

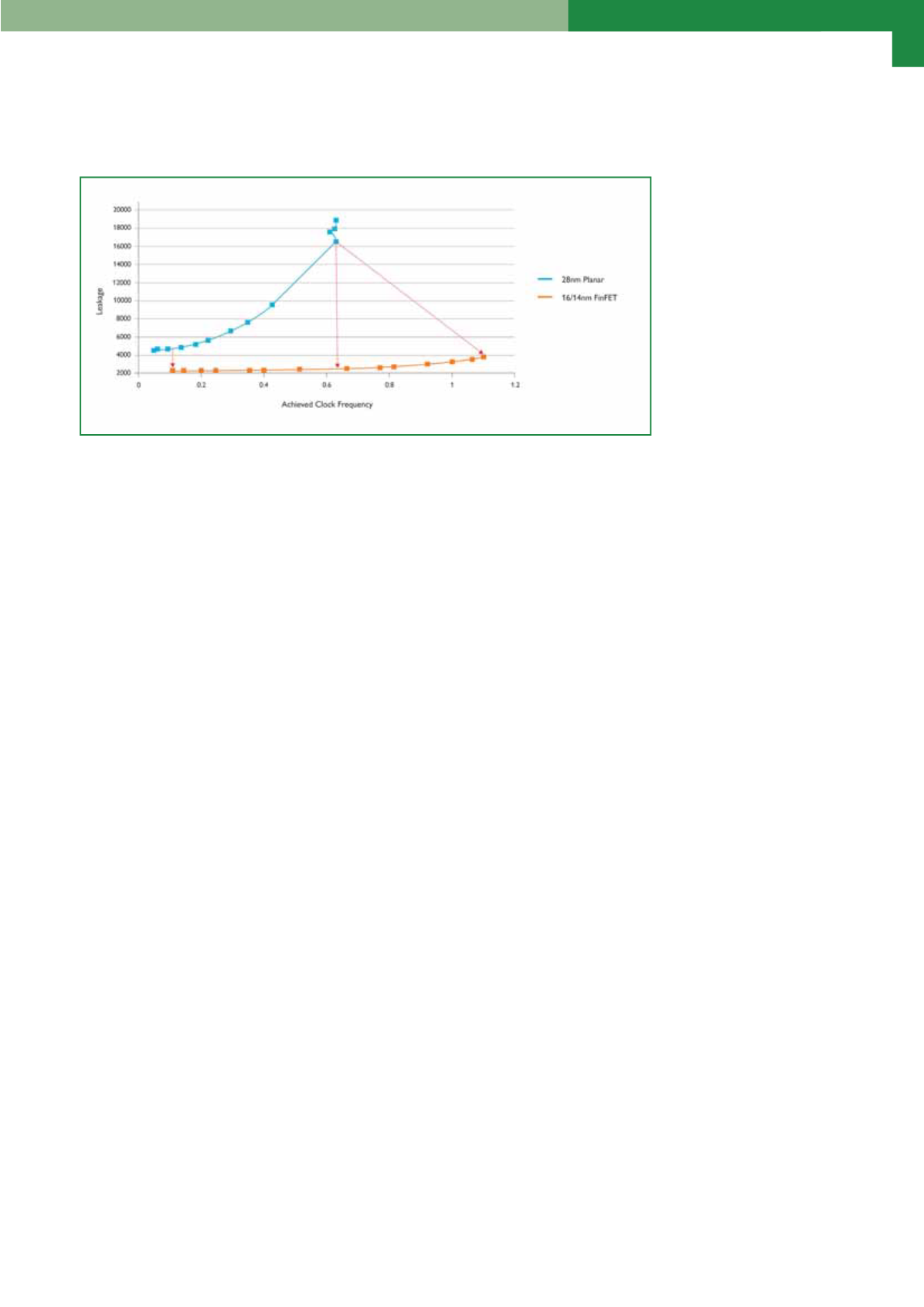

Fig. 1 – I transistor finFET da 16/14 nm garantiscono un miglior controllo delle perdite sull’intero intervallo

di frequenza