Mentor Graphics estende Catapult C con il supporto per la control logic

Questa tecnologia innovativa consente ai progettisti di utilizzare puro Ansi C++ sia per la codifica dei blocchi algoritmici sia per quella dei blocchi relativi alla control logic.

L’estensione delle funzionalità del tool Catapult C per la HLS (High Level Synthesis) full-chip è di fondamentale importanza, alla luce della rapida espansione dei progetti sia in termini di dimensioni che di complessità, che costringe gli ingegneri a progettare funzionalità hardware a livelli di astrazione sempre più elevati.

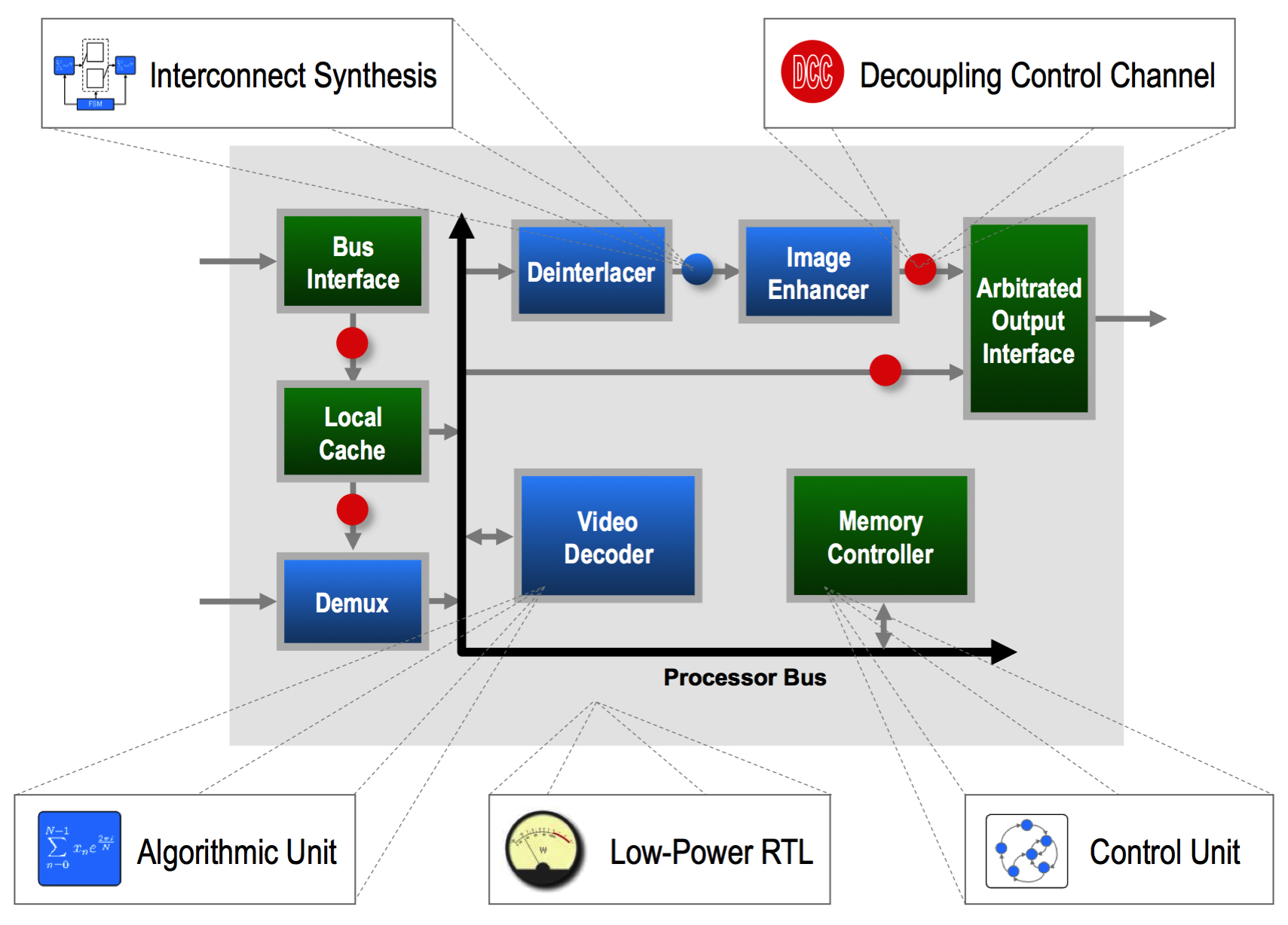

Tradizionalmente, la sintesi della control logic e la sintesi algoritmica sono state affrontate separatamente, utilizzando linguaggi differenti, come pure differenti formalismi e astrazioni. Le recenti innovazioni introdotte nel tool di sintesi Catapult C unificano questi due domini, consentendo ai progettisti di descrivere la control logic unitamente al comportamento algoritmico in un modello unico e coerente, utilizzando codice Ansi C++ standard.

Al centro di questa innovazione vi è un nuovo costrutto C++ sintetizzabile, che consente ai progettisti di specificare in modo semplice un trasferimento di dati mediante comunicazioni asincrone, mantenendo il controllo completo sulla creazione di hardware concorrente. Questo meccanismo chiave permette di interfacciare le rappresentazioni algoritmiche guidate dal flusso dati con i blocchi di controllo sincronizzati dai clock. Ne risulta uno stile di codifica familiare ai progettisti hardware, che consente agli utenti di esprimere facilmente il coordinamento delle comunicazioni, delle priorità e dei task all’interno di una rappresentazione astratta della concorrenza. Questo nuovo approccio formalizza uno stile di modellizzazione che è dotato della precisione indispensabile per i task relativi al controllo, ma è anche capace di mantenere quelle caratteristiche di astrazione preziose per i sottosistemi algoritmici.

Il processo di sintesi è affiancato da un flusso di verifica in attesa di brevetto, completamente automatizzato, che per la prima volta permette agli utenti di validare in modo dettagliato a livello C le interazioni tra i blocchi di livello RTL. La stretta integrazione tra verifica e sintesi si è rivelata indispensabile per esprimere tutto il potenziale della HLS. Uno dei trabocchetti in cui si cade comunemente, lavorando con altri tool di HLS, consiste nello sviluppo della HLS in modo isolato, con una conseguente esplosione della complessità della verifica dell’output RTL.

“Tipicamente, i nostri IC di digital broadcasting consistono in un complesso mix di unità algoritmiche, molto onerose dal punto di vista computazionale, e di blocchi dedicati al controllo”, sostiene il professor Schlicht, capo del Dipartimento Circuiti Integrati del Fraunhofer Institute. “Le nuove estensioni di Catapult per la sintesi della control-logic ci consentono di sviluppare una maggiore frazione del sistema complessivo utilizzando la High-Level Synthesis in C++. Ciò ci permette di estendere il nostro flusso di implementazione in C++ al di là dei blocchi di puro signal processing”.

In aggiunta al supporto per la control logic, il tool di sintesi Catapult C include ora anche una tecnologia innovativa per la progettazione low-power, che applica automaticamente due tecniche progettuali tra le più usate: il clock gating multilivello e l’interfacciamento a unità di gestione dinamica della potenza e dei clock. Il tool Catapult C è in grado di analizzare in profondità gli alberi logici per trovare i clock a cui poter applicare il gating, un’attività tipicamente effettuata da progettisti esperti di backend low-power in modo manuale e quindi onerosa e soggetta a elevati tassi di errore. Questa ottimizzazione, nuova e unica, produce risultati di clock gating con una precisione vicina al 100%, operando a livello dei flip-flop e massimizzando i risparmi di potenza grazie a una tecnica di inferenziazione locale della logica di gating nelle dirette vicinanze dei registri presi in oggetto. Inoltre, per consentire ulteriori riduzioni di power, il tool di sintesi Catapult C esporta in real-time le informazioni sullo stato di tutti i blocchi del sistema. Questa informazione viene passata alle unità di power management, per alimentare le logiche euristiche di frequency e voltage scaling dinamici, con conseguenti riduzioni di power a livello di sistema. La riduzione dinamica di potenza, come prevedibile, dipende sia dal progetto che dai vettori ti test; le rilevazioni effettuate su oltre 300 progetti di clienti di Mentor Graphics hanno evidenziato miglioramenti variabili tra il 10% e il 90%, con una media pari al 40%.

“Le estensioni di Catapult C per la control logic ora ci consentono di sviluppare una porzione maggiore dei nostri sistemi mediante la HLS,” afferma Emmanuel Liegeon, Deputy Manager del Digital ASIC & FPGA Design Group di Thales Alenia Space. “Con l’aumento della frazione del sistema che sviluppiamo in HLS, diventa inoltre sempre più cruciale la gestione dell’aspetto power. Le recenti migliorie introdotte in Catapult C per il low-power producono le ottimizzazioni di cui abbiamo bisogno”.

Disponibilità

www.mentor.com/products/esl/catapult-c

Mentor Graphics

www.mentor.com

Contenuti correlati

-

Phoenix Contact aderisce a Orgalim

Phoenix Contact ha aderito a Orgalim, la più grande organizzazione ombrello per la tecnologia industriale in Europa. L’obiettivo è quello di sostenere l’associazione nel suo lavoro di comitato europeo e, a tal fine, Phoenix Contact introdurrà approcci...

-

Illuminazione automotive differenziata con la tecnologia MeLiBu di Melexis

La tecnologia MeLiBu di Melexis , con i relativi IC driver, offre una piattaforma altamente flessibile e completamente scalabile per differenziare le applicazioni di illuminazione nei veicoli. Si tratta di una combinazione di IC driver multicanale e...

-

Come la tecnologia sta trasformando gli ospedali

Con le risorse sempre più limitate, i prestatori di assistenza sanitaria si stanno rivolgendo alla tecnologia per aumentare la capacità e migliorare i risultati per i pazienti Leggi l’articolo completo su EO Medical 21

-

Xilinx: 30 anni di tecnologia innovativa

La società di San Jose, nota, fra l’altro, per i suoi FPGA e il modello fabless, ha festeggiato i suoi primi 30 anni di innovazioni e brevetti (3500). Le innovazioni hanno trasformato questa azienda specializzata in logica...

-

Sensori wireless, il mercato esploderà entro il 2019

Secondo il report di Electronics.ca “Wireless Sensor Network Market Shares, Strategy, and Forecasts, Worldwide, 2013 to 2019” i mercati mondiali di sensori wireless sono pronti a raggiungere una crescita significativa, in quanto viene utilizzato il Wireless Sensor Network...

-

ITE Day 2013, la tecnologia diventa efficiente

Si è conclusa registrando una buona affluenza di pubblico la prima edizione di ITE day, mostra convegno organizzata da Fiera Milano Media con la collaborazione di Business International all’ATAHotel Expo Fiera di Pero (MI) dedicata al tema dell’efficienza...

-

I progressi nella tecnologia produttiva MEMS che guidano la crescita industriale

La prossima generazione di dispositivi basati sulla tecnologia MEMS, TSVs, fotonica e altre, richiederà tecnologie di fabbricazione avanzate, ma anche costi ridotti e un rapido ritorno sull’investimento per i produttori

-

La progettazione elettronica con la tecnologia Altium Vault

La piattaforma Altium Designer rende più omogenea ed elegante la gestione dei dati di progetto e semplifica il riutilizzo dei sistemi

-

Tecnologia di generazione delle forme d’onda Trueform

Jitter delle forma d’onda significativamente inferiore e capacità di ottenere una rappresentazione esatta della forma d’onda desiderata, anziché una sua approssimazione, sono alcuni dei vantaggi della tecnologia Trueform

-

La tecnologia DDC di SuVolta

In occasione dell'IEDM 2011, SuVolta ha annunciato nuovi dettagli sulla sua tecnologia DDC e con Fujitsu Semiconductor ha dimostrato il funzionamento di SRAM operanti a 0,4 V.