Memorie Sram che dimezzano i consumi grazie a un attento layout

La più bassa tensione operativa delle nuove Sram di SureCore consente di integrarle nei chip allacciandole alla stessa rete di alimentazione dei core CPU riducendo la complessità circuitale e migliorando l’efficienza energetica dei sistemi

La giovane società inglese SureCore ha sviluppato una tecnologia che consente di dimezzare il consumo delle celle di memoria statiche ad accesso casuale, Sram, senza aumentarne le dimensioni sul silicio né diminuirne la velocità di commutazione. Oltre all’inferiore potenza elettrica utilizzata questa tecnologia offre anche due ulteriori importanti vantaggi che sono, innanzi tutto, l’implementazione nei processi di fabbricazione standard in geometria di riga da 28 nm e, in secondo luogo, la possibilità di lavorare con una tensione più bassa rispetto a quella tipicamente in uso per le Sram e provvidenzialmente comparabile con quella dei circuiti logici.

Ciò significa che con questa tecnologia diventa possibile utilizzare una sola alimentazione per le memorie e per le unità di calcolo e così si evita di dover implementare due convertitori dc/dc e due reti di distribuzione della potenza per raggiungere i due tipi di elementi spesso integrati in diverse aree funzionali dei chip come succede nei moderni multicore che hanno tipicamente svariate Sram embedded per le cache L1 e L2, per i coprocessori e per i buffer delle periferiche.

Le memorie Sram SureCore consumano meno perché abbattono l’energia inutilizzata e pertanto possono lavorare con la stessa tensione di alimentazione dei circuiti logici

Questo vantaggio è particolarmente importante per i sistemi di piccole dimensioni che si rivolgono alle moderne applicazioni a basso consumo come i prodotti per Internet-of-Things, i dispositivi elettronici indossabili, le reti distribuite di sensori e naturalmente i terminali mobili che vedrebbero sensibilmente allungare la durata delle batterie.

Celle statiche ma veloci

Le nuove celle Sram brevettate da SureCore sono state progettate con un’architettura particolarmente efficiente e perfezionate con un’approfondita analisi circuitale che ne ha definito le caratteristiche confermate nei test che dimostrano l’effettiva diminuzione dei consumi del 50% rispetto alle attuali Sram. Per di più, queste celle hanno un disegno molto semplice e oltre che con i transistor CMOS standard possono essere realizzate anche con i nuovi transistor Fin-FET e FD-SOI che promettono di farne scendere ulteriormente la geometria di riga a 22 e persino a 16 nm.

Come è noto le memorie Sram conservano i dati solo mentre sono alimentate e dentro i chip multicore sono preferite alle Dram perché non hanno bisogno di refresh. Oggi le Sram occupano tipicamente la metà del silicio di un chip e talvolta anche un po’ di più e poiché le singole celle sono costituite da sei o otto transistor si capisce che diminuirne la tensione di lavoro significa abbassare notevolmente i consumi per l’intero sistema circuitale.

In genere, per controllare la distribuzione della potenza nei chip spesso viene impiegata dai costruttori la tecnologia Dynamic Voltage and Frequency Scaling, DVFS, che serve a diminuire temporaneamente la frequenza e la tensione nelle aree del chip non utilizzate tutte le volte che ciò sia possibile, ma se la tensione può essere azzerata nei circuiti logici non può esserlo nelle Sram che al di sotto di una soglia minima perderebbero i dati immagazzinati. Il vantaggio di avere una tensione più bassa sulle celle delle Sram è quindi fondamentale per l’intero sistema, ma solo a patto che sia adeguata per conservare i dati e sufficiente per non generare instabilità.

Una tipica cella Sram con una coppia di inverter e due transistor di comando ha una dissipazione che dipende dalle capacità parassite ma anche dalla posizione che occupa nell’array di memoria

Una tendenza comune ai progettisti di sistemi multifunzionali integrati è quella di affiancare sul silicio una piccola Sram ad ogni funzione e implementarne quindi anche una decina spargendole nelle diverse aree funzionali del chip. Il motivo è che in genere la quantità dati immagazzinabile è inversamente proporzionale alla velocità di lettura o scrittura e quindi succede che le memorie grandi sono più lente e quelle piccole sono più veloci.

Questo approccio migliora le prestazioni ma costringe a disegnare due reti di distribuzione della potenza di alimentazione ossia una a tensione inferiore per i circuiti logici e una a tensione più alta per le Sram, complicando il layout proprio perché questi due sottosistemi sono sparsi dappertutto nel chip. Le nuove Sram con tensione più bassa potrebbero almeno in alcune aree del chip allacciarsi alla rete di alimentazione dei circuiti logici e consentire di eliminare una gran quantità di piste sul silicio.

D’altro canto, ridurre la tensione di lavoro alle geometrie di riga di 28 nm e ancor meno significa creare fluttuazioni elettromagnetiche del rumore di cui bisogna tenere conto trovando il miglior equilibrio fra lo Static Noise Margin che misura l’abilità di conservare integri i dati e il Write Noise Margin che misura l’abilità di modificare i dati immagazzinati. In ciò si sono focalizzate le ricerche degli esperti SureCore che hanno poi capito come abbassare la tensione operativa minima senza penalizzare i parametri SNM e WNM e senza aumentare il numero dei transistor per cella.

Cariche sotto controllo

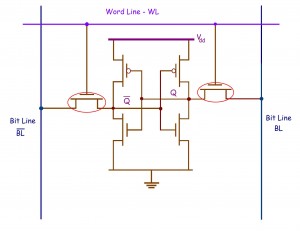

Le celle Sram hanno quattro transistor che formano una coppia incrociata di invertitori che obbedisce a due transistor di comando laterali che si allacciano al di sopra con una Word Line (WL) e ai fianchi con due Bit Line (BL e BL). Quando la WL principale è spenta allora i due transistor disconnettono la cella dalle bit line e i due inverter si compensano a vicenda mantenendo lo stato in cui si trovano, ossia l’1 o lo 0. La lettura avviene caricando entrambe la BL e la BL a 1 e poi attivando la word line in modo tale che il bit contenuto nella cella attivi solo l’inverter di carica opposta che di conseguenza va a scaricare la bit line di opposto valore.

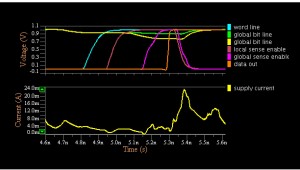

La simulazione di un ciclo continuo di lettura con clock di 1 GHz mostra di limitare la corrente alla minima necessaria e i consumi al di sotto di 6 mW

Se c’era uno 0, dunque, la BL si scarica a 0 e la BL rimane precaricata a 1 e viceversa se c’era 1 si scarica la BL mentre la BL rimane a 1. La scrittura avviene impostando il valore che si vuole scrivere nella BL e il suo opposto nella BL e poi attivando la WL per accendere i due pass transistor che fanno scattare i due inverter in opposizione in modo tale che nella cella rimanga il valore della BL.

Dunque, oltre a conservare l’1 e lo 0, la cella può leggere uno 0, leggere un 1, scrivere uno 0 e scrivere un 1 e in ciascuna di queste quattro operazioni si instaura una diversa sequenza di commutazione da parte dei sei transistor. Tuttavia, ogni commutazione implica uno spostamento di carica nei transistor e questa carica si accoppia con la differenza di potenziale applicata generando una dissipazione di energia proporzionale alla capacità parassita equivalente propria di ogni transistor.

L’energia generata nell’i-esimo transistor a causa del movimento della carica si può definire come Ei = niΔQiVdd dove ni è il numero dei cambiamenti di stato, ΔQi è la carica contenuta e Vdd è la tensione di alimentazione responsabile di attivare la dissipazione di energia. Inoltre, la carica può scriversi come CiΔVi e cioè con il valore della capacità parassita moltiplicato per la differenza di potenziale ivi applicata. Pertanto, l’energia totale dissipata diventa la sommatoria:

E = Σi Ei = Σi ni CiΔVi Vdd = Vdd Σi niCiΔVi

Si capisce che alla dissipazione contribuiscono tutti e tre i fattori ni , Ci e ΔVi ma ciascuno in diverso modo ed è proprio su quest’aspetto che hanno lavorato a lungo i ricercatori SureCore riuscendo a diminuirli laddove era più conveniente. Per esempio nei due pass transistor di comando la Ci e la ΔVi sono più grandi mentre la ni è più piccola e perciò anche se sono in minor numero le commutazioni ingenerano maggior energia parassita dissipata.

Nei transistor degli inverter le commutazioni sono più frequenti ma a parità di valore delle capacità parassite diminuisce la differenza di potenziale applicata e, di conseguenza, l’energia dissipata è inferiore a quella precedente relativamente a ogni singola commutazione, ma considerando complessivamente tutti i transistor della cella diventa la componente più importante perché gli inverter effettuano un maggior numero di commutazioni rispetto ai pass transistor. Infine, c’è una piccola percentuale di energia dissipata che dipende poco dalla capacità parassita e più dalla variazione della tensione ed è quasi uguale in tutti e sei i transistor ma diminuisce con la distanza della cella dalla periferia verso il centro dell’array di memoria.

Gli esperti SureCore hanno sapientemente individuato i valori ottimi di ni , Ci e ΔVi in ciascuna area circuitale della memoria riducendone il valore più significativo nei transistor con un opportuno disegno delle piste a seconda della posizione che occupano nell’array. Oltre a ciò, i progettisti SureCore hanno introdotto la tecnologia brevettata Active Bit Line Enable (ABLE) che consiste in una rete supplementare di transistor che si occupano di individuare e isolare le celle inattive o poco utilizzate per assegnare loro una condizione di standby nella quale non vengono alimentate ma possono comunque essere riattivate all’occorrenza.

Questo fattore è importante perché abbatte la dispersione dell’energia inutilizzata che costituisce una buona parte dell’energia totale dissipata. L’attento layout e la tecnologia ABLE consentono di abbattere la dissipazione a circa la metà e le sperimentazioni dimostrano che si può far lavorare una memoria da 4k x 72 bit (ossia 288 kbit) in lettura e scrittura al clock di 1 GHz consumando meno di 6 mW.

Lucio Pellizzari

Contenuti correlati

-

Dispositivi di memoria per sistemi embedded, le opportunità della MRAM

Il sistema di memorizzazione basato su tecnologia magnetoresistiva è di tipo non volatile e fornisce diversi benefici rispetto alle convenzionali memorie SRAM e DRAM. In virtù delle proprie caratteristiche, la tecnologia MRAM può soddisfare differenti casi d’uso in...

-

Cypress: nuove SRAM asincrone con ECC on chip per garantire una maggiore affidabilità

Cypress Semiconductor ha annunciato i primi campioni di una nuova SRAM asincrona veloce con ECC (Error-Correcting Code). Il circuito ECC presente a bordo del chip garantisce i più elevate livelli di affidabilità dei dati senza dover ricorrere...

-

MRAM: crescita boom entro fine decennio secondo Coughlin Associates

La magnetic RAM (MRAM) potrebbe avere un’impennata da qui al 2020 grazie al fatto che sta sostituendo perfettamente DRAM e SRAM. Secondo un rapporto di Coughlin Associates, oltre ai risparmi derivanti da operazioni senza richieste di alimentazioni...

-

sureCore riceve fondi per lo sviluppo di memoria a basso consumo

Incentivi per 250K di sterline a sureCore per realizzare una tecnologia di memoria SRAM a bassa potenza. Il contributo sarà utilizzato per lo sviluppo di un chip che sarà utilizzato per mostrare il controllo dell’array brevettato sureCore...

-

Renesas e Segger: software commerciale gratuito per progetti basati sulla piattaforma di μc a 32-bit RX

Renesas Electronics Europe e Segger Microcontroller offrono un innovativo programma di supporto software per i clienti europei. I clienti possono beneficiare di un pacchetto gratuito di software commerciale di Segger Microcontroller, fino al valore di 20.000 euro,...

-

Accordo di distribuzione globale tra Alliance Memory e Mouser Electronics

Alliance Memory, produttore di memorie di tipo legacy per i settori delle telecomunicazioni, informatico, industriale e consumer, ha raggiunto un accordo di distribuzione con Mouser Electronics. In base ai...

-

Actel corteggia il mercato ‘handheld’

La società punta a diffondere gli Fpga flash-based nei terminali mobile usati in campo medicale, industriale e consumer