Memoria grafica dei dispositivi indossabili: alcune considerazioni

Anche se per le operazioni di frame buffering il tipo di memoria più usato è la DRAM, vi è un rinnovato interesse per le memorie SRAM grazie alla richiesta di alte prestazioni e, soprattutto, di diminuzione dei consumi da parte dei dispositivi portatili e indossabili delle prossime generazioni

La fruizione di media (o mezzi di comunicazione) ad alta definizione sta aumentando su due fronti: da un lato si assiste a un incremento del numero di consumatori mentre dall’altro si osserva una crescente richiesta di contenuti caratterizzati da una definizione ancora più spinta. Ciò è dovuto alla sempre più massiccia penetrazione di Internet, alla possibilità di accedere alla Rete a velocità sempre più spinte e alla crescita esponenziale del numero di dispositivi mobili. Di conseguenza, molti dispositivi indossabili sono ora in grado di gestire questo “consumo” di media ad alta definizione.

Le stime più prudenti indicano che la richiesta di dispositivi indossabili e per IoT (Internet of Things) è destinata a triplicare da qui al 2020, anno in cui è previsto ci saranno in circolazione circa 50 miliardi di dispositivi di questo tipo. Ciò alimenterà la richiesta di nuove famiglie di circuiti di pilotaggio per display (display driver) e di frame buffer – un’opzione di memoria differente da quella utilizzata nei display “legacy”.

Mentre le memorie RAM embedded potrebbero risultare sufficienti per i dispositivi indossabili delle prime generazioni, quelli odierni dispongono di display ad alta definizione di ampie dimensioni che richiedono frame buffer (che contiene l’immagine da visualizzare) di dimensioni sensibilmente maggiori. Questi requisiti sono molto diversi da quelli dei tradizionali display dei PC e degli apparecchi televisivi in quando i dispositivi indossabili sono alimentati a batteria e l’efficienza energetica è il vincolo di progetto più importante.

La maggior parte dei dispositivi indossabili di prossima introduzione dovranno essere caratterizzati da dimensioni e consumi estremamente ridotti in modo da poter funzionare per giorni, se non addirittura per settimane, con una singola carica pur dovendo eseguire operazioni anche molto complesse. Questo è il motivo per cui è necessario ricorrere a circuito per il pilotaggio dei display di nuova concezione.

Sistemi grafici: nozioni di base

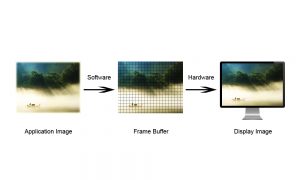

Per comprendere i requisiti dei frame buffer utilizzati nei dispositivi indossabili, è utile dapprima una breve analisi dei sistemi grafici. Ogni sistema grafico è formato da tre elementi: hardware, librerie grafiche e un’applicazione che la utilizza. Mentre la libreria e l’applicazione sono controllate dal software, l’hardware è controllato da un frame buffer, una memoria che si distingue per l’elevato throughput.

Ciascun elemento del frame buffer corrisponde a un singolo pixel sullo schermo. L’intensità di quel pixel è determinata dalla sua tensione.

La risoluzione di un display è definita da tre elementi:

- Numero di linee di scansione

- Numero di pixel per linea

- Numero di bit per pixel

Se si considera un’immagine a 24 bit e una risoluzione di 1024×760 pixel, quella più diffusa nel mondo PC, la capacità minima del frame buffer richiesta per supportare questo tipo di display è pari a: 1024x768x24 = 18,9Mb

La disponibilità di una memoria di queste dimensioni da sola non è sufficiente nel caso di un display dinamico con funzionalità video. Per questo motivo è necessario prendere in considerazione il throughput dei frame buffer.

Per un video a 30 fps (frame per second) con risoluzione pari a quella indicate in precedenza, il throughput massimo sarà pari a 18,9×30 = 566 Mbps.

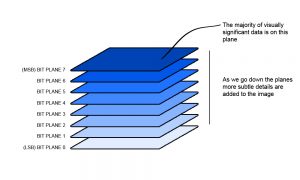

Ogni cella di memoria in un frame buffer corrisponde a un singolo pixel. Nel caso di un display a colori di n bit, ciascuno di questi n bit è un bit plane (piano di bit) separato: un colore a 24 bit avrà 24 bit plane (Fig. 2). Quindi saranno necessarie n celle per memorizzare lo stato di ciascun pixel. I valori binari di ciascuno degli n piani di bit sono caricati nelle posizioni corrispondenti in un registro. Il numero binario risultante è interpretato come un livello di intensità compreso tra 0 e 2n-1. Esso è quindi convertito in una tensione analogica di valore compreso tra 0 e il valore massimo mediante un convertitore D/A: i livelli di intensità sono dunque pari a 2n.

Fig. 2 – In un display a colori a n bit, ciascuno di questi n bit e un piano di bit separato (Fonte: National Programme on Technology Enhanced Learning, India)

Criteri di scelta

Sono due gli elementi che concorrono a determinare il tipo di frame buffer utilizzato per un display: dimensione e throughput. L’aumento della risoluzione di un’immagine richiede più memoria mentre l’incremento della frequenza di acquisizione e/o riproduzione dei fotogrammi (fps) richiede un throughput più alto. Per soddisfare questi requisiti esistono due alternative: minimizzare le dimensioni del frame buffer e ottimizzare il throughput oppure aumentare al massimo le dimensioni del frame buffer per minimizzare il throughput (in pratica un parametro raddoppia mentre l’altro viene dimezzato). Con l’aumento delle dimensioni del frame buffer (che in pratica significa integrare più frame buffer in un singolo chip) è possibile ridurre il throughput grazie alla riduzione del numero dei cicli di ingresso-uscita.

Raddoppiando le dimensioni, ad esempio, è possibile memorizzare due fotogrammi simultaneamente in un singolo buffer, in modo da dimezzare il numero di chiamate/riferimenti al buffer in un certo intervallo di tempo, ottenendo in tal modo una riduzione del throughput. Esistono quindi due tipi di opzioni di memoria: quelle ad alta densità e quelle a elevato throughput.

Un’analisi più dettagliata delle specifiche delle GPU (Graphic Processing Unit) delle più recenti generazioni di Nvidia e AMD evidenza la disponibilità di memorie di ampie dimensioni, spesso dell’ordine dei Gigabyte. Ciò è dovuto al fatto che molte di queste GPU sono destinate ad applicazioni quali videogiochi e rendering ad alta definizione, e prevedono una serie di funzionalità aggiuntive che occupano parecchio spazio in memoria – MSSA (Multi-Sampled Anti-Aliasing), pre-fetching, shadow buffers (che permette di presentare ombre in tempo reale e più realistiche), rendering differito ed effetti speciali.

Anche le funzionalità più comuni, come ad esempio lo scrolling in modalità “windowed” richiedono spazio aggiuntivo del buffer. Parecchi buffer utilizzati nell’ambito dei videogiochi utilizzano la bufferizzazione tripla (ovvero tre buffer per ogni fotogramma) e la tecnica HDR, ovvero la visualizzazione di scene ad elevato range dinamico (la profondità dell’HDR è 64 bit invece di 24). Molte di queste GPU di fascia alta supportano più display ad alta definizione, il che implica la presenza di un buffer interno dedicato per ciascuno di questi display.

Tutte le caratteristiche appena sopra delineate non sono richieste nella maggior parte dei dispositivi indossabili e portatili a causa delle ridotte dimensioni dei loro display. L’approccio ideale sarebbe quello di utilizzare le risorse della memoria integrata della MCU come frame buffer. Ciò garantisce il più elevato throughput a fronte della massima semplicità di implementazione. Molte CPU non dispongono di una memoria di dimensioni sufficiente per supportare i display di ultima generazione dei dispositivi indossabili. Senza dimenticare che la crescente complessità dei programmi richiede che uno spazio sempre maggiore della memoria integrata sia utilizzata come cache di primo livello (L1) della MCU.

La maggior parte dei dispositivi indossabili dell’attuale generazione è dotata di display con risoluzione QVGA (Quarter Video Graphic Array). Per display di questo tipo le specifiche più comuni sono: 24 bit, risoluzione 480 x 360 e velocità di 30 fps. Ciò si traduce in una densità di pixel (PPI – Pixel Per Inch) pari a 300 per i display dei dispositivi indossabili. I requisiti per questo tipo di display prevedono una memoria di 4 Mb con un throughput pari a 120 Mbps. I futuri dispositivi saranno dotati di display con risoluzione molto più elevata, con densità di pixel di 400 ppi, come molti telefoni cellulari delle ultime generazioni. L’amento della densità di pixel a parità di dimensioni del display implica un corrispondente incremento delle dimensioni del frame buffer.

Come già spiegato in precedenza, esistono due modalità per implementare un frame buffer di queste dimensioni: un buffer da 4 Mb con un throughput di 120 Mbps o un buffer di 16 Mb con un throughput di 30 Mbps. Tra le due alternative, quella che prevede un buffer di dimensioni inferiori può vantare molteplici benefici: ingombro più ridotto (nel caso di implementazioni sotto forma di die o Csp), minor consumo di potenza, costo inferiore e disponibilità di un maggior numero di opzioni (a un aumento della densità corrisponde una diminuzione del numero di costruttori e di versioni). Nel caso dei dispositivi indossabili, ingombri, consumi e costo sono i criteri che determinano la scelta dei componenti di un dispositivo.

DRAM vs SRAM

Per le operazioni di frame buffering il tipo di memoria più usato è la DRAM (Dynamic RAM), nonostante il fatto che la memoria ad alte prestazioni disponibile su più larga scala attualmente è la SRAM (Static RAM). Rispetto alle RAM statiche, quelle dinamiche sono caratterizzate da consumi più elevati e throughput inferiore. Anche se contraddistinte da migliori prestazioni, quindi ideali per i dispositivi portatili delle più recenti generazioni, le RAM statiche non sono usate in un gran numero di prodotti con batteria di backup.

Ciò è dovuto al fatto che l’offerta per questo tipo di memorie è abbastanza limitata: le SRAM statiche sono infatti disponibili in modelli a bassa densità, fino a 128 MB. La struttura di una cella di memoria di una RAM statica, che prevede 6 transistor, è più complessa rispetto a quella di una RAM dinamica, formata da 1 transistor e 1 condensatore. Questo è il motivo per cui l’implementazione di RAM statiche con densità più elevate risulta difficile.

Nonostante tale limitazione abbia precluso l’utilizzo di RAM statiche nei dispositivi consumer “legacy” (personal computer, apparecchi televisivi e telefoni cellulari), esse possono trovare spazio nei dispositivi indossabili, in considerazione del fatto che l’operazione di frame buffering richiede memorie di ridotte dimensioni. Nel caso delle SRAM, le maggiori prestazioni (un throughput più elevato corrisponde a minori consumi) rappresentano un indubbio vantaggio.

Considerate quasi estinte, le SRAM sembrano destinate a una seconda giovinezza grazie alla richiesta di alte prestazioni e, soprattutto, di diminuzione dei consumi da parte dei dispositivi indossabili.

Molti dei principali produttori di memorie RAM statiche hanno sviluppato una serie di innovazioni per soddisfare in particola modo le richieste provenienti dal mercato dei sistemi indossabili – dalla maggiore affidabilità all’implementazione di nuovi tipi di package. Azienda di riferimento nel settore delle SRAM, Cypress è una protagonista nel mercato dell’Internet of Things, proponendo una gamma di memorie che spazia dai modelli che garantiscono la più elevata affidabilità a quelli offerti in package Cps (Chip Scale Package) di dimensioni miniaturizzate.

Reuben George, Cypress Semiconductor

Contenuti correlati

-

Monitoraggio dei processi industriali con il microcontrollore ESP32

Un sistema di monitoraggio dei processi industriali è molto utile per la piccola e media industria per ottenere il massimo rendimento della produzione ed evitare guasti ai macchinari e incidenti. Un sistema di monitoraggio e sicurezza semplice...

-

Soluzioni modulari configurabili per semplificare la personalizzazione delle HMI

Con le sue soluzioni modulari configurabili, SECO assicura il perfetto equilibrio tra disponibilità immediata e configurabilità, venendo incontro alle esigenze eterogenee dei clienti e riducendo al tempo stesso i costi NRE Leggi l’articolo completo su EMB92

-

Sistemi operativi real-time: 6 RTOS per applicazioni embedded più sicure

I progetti nel settore automobilistico, nell’automazione industriale, nella sanità, ma anche nel mondo Internet of Things, si stanno focalizzando maggiormente sui requisiti di sicurezza dei sistemi critici. Questo trend sta spingendo i vendor di piattaforme RTOS a...

-

Apprendimento automatico alla periferia della rete: le considerazioni chiave per sviluppare un progetto sostenibile

Numerosi sistemi embedded, in particolare quelli utilizzati nelle installazioni IoT (Internet of Things) ubicate alla periferia della rete (edge), integrano algoritmi di apprendimento automatico (ML – Machine Learning). Mark Patrick, responsabile del Technical Marketing per la regione...

-

Intelligenza Artificiale e Internet of Things (AIoT) uniti per le soluzioni industriali

Una panoramica sull’AIoT, ovvero la convergenza dell’IA e dell’IoT nel settore della produzione industriale Leggi l’articolo completo su Embedded 89

-

Device IoT e tecnologia operativa, sempre più presi di mira dal cybercrime

Le vulnerabilità dei dispositivi OT e Internet of Things sono sfruttate in modo crescente dai criminali informatici per penetrare in reti industriali e infrastrutture critiche. Quali tecniche di protezione e misure sono attuabili per la mitigazione delle...

-

Il ruolo delle MCU a 8 bit nel controllo delle applicazioni IoT

Risalendo all’indietro nel tempo fino agli anni ’70, i microcontrollori hanno svolto un ruolo di primo piano nel controllo di una gran varietà di prodotti destinati ai settori automotive, consumer e industriale. Oggi, questo ruolo si è...

-

Guida tecnica ai convertitori dati

La conversione dei dati è una funzione essenziale che collega il mondo analogico a quello digitale. La conversione da analogico a digitale e da digitale ad analogico è presente nella maggior parte dei sistemi embedded. Dai sensori...

-

Software safety-critical, servono strumenti evoluti di test e validazione

L’aumento della complessità del codice embedded e la crescente pressione competitiva creano una “tempesta perfetta” per gli sviluppatori di software safety-critical, ad esempio, nel settore automotive. Ma l’adozione di tool avanzati, e la riorganizzazione dei team di...

-

Le comunicazioni nei sistemi embedded IoT ESP32

In questo articolo verrà fornita una panoramica sulle comunicazioni dei sistemi embedded IoT attraverso la descrizione dei protocolli standard di comunicazione e di un sistema embedded IoT rappresentato dalla scheda di sviluppo ESP32 DevkitC costituita dal modulo...