Da Cadence il sistema di implementazione Innovus

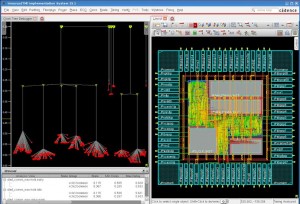

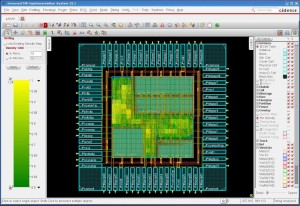

Cadence Design Systems ha presentato Cadence Innovus Implementation System, la soluzione di implementazione fisica di nuova generazione che consente agli sviluppatori di system-on-chip (SoC) di realizzare progetti con caratteristiche all’avanguardia in termini di potenza, prestazioni e area (PPA) e di accelerare contemporaneamente il time to market. Basato su un’architettura ad elevato parallelismo e su tecnologie di ottimizzazione innovative, il sistema di implementazione Innovus offre in genere livelli di PPA dal 10 al 20 percento superiori, a fronte di un incremento tipico da 5 a 10 volte della capacità e della velocità di sviluppo full-flow su nodi di processo tradizionali e su FinFET avanzati da 16/14/10nm.

Il sistema di implementazione Innovus è stato concepito con diverse funzionalità chiave per aiutare gli ingegneri di progettazione fisica ad ottenere prestazioni al vertice o a conseguire il massimo risparmio in termini di potenza/area ottimizzando lo sviluppo per una frequenza target predeterminata.

Il sistema di implementazione Innovus è stato concepito con diverse funzionalità chiave per aiutare gli ingegneri di progettazione fisica ad ottenere prestazioni al vertice o a conseguire il massimo risparmio in termini di potenza/area ottimizzando lo sviluppo per una frequenza target predeterminata.

Le funzionalità chiave offerte da Innovus per raggiungere questo obiettivo sono:

- la nuova tecnologia di posizionamento “solver-based” GigaPlace, dove il placement è pilotato dallo “slack” e tiene conto di topologia, accesso ai pin e colore. Tale tecnologia consente di raggiungere risultati ottimali in termini di posizionamento delle pipeline, di lunghezza dei percorsi, di utilizzo e di PPA, garantendo il miglior punto di partenza per l’ottimizzazione

- l’ottimizzazione avanzata multi-threaded e layer-aware pilotata da considerazioni di potenza e temporizzazione, la quale riduce i consumi dinamici e le perdite garantendo prestazioni ottimali

- l’ottimizzazione concorrente di clock e datapath, unica nel suo genere, che include la generazione automatica di H-tree ibridi per migliore la variabilità cross-corner e spingere le prestazioni al massimo riducendo i consumi

- un routing slack-driven di nuova generazione con ottimizzazione delle temporizzazioni che tiene conto dei percorsi e affronta preliminarmente gli aspetti d’integrità del segnale migliorando la correlazione post-route

- una tecnologia multi-obiettivo su tutto il flusso di sviluppo che consente l’ottimizzazione elettrica e fisica concomitante per evitare squilibri locali, garantendo un approccio PPA più globale

Il sistema di implementazione Innovus offre anche molteplici funzionalità che potenziano i tempi di completamento di ogni iterazione di place-and-route. I suoi algoritmi di base sono stati migliorati con prestazioni multi-threading su tutto il flusso, assicurando un notevole aumento di velocità anche con hardware standard che utilizzano da 8 a 16 CPU. Inoltre, il sistema di implementazione Innovus rappresenta la prima soluzione distribuita ad elevato parallelismo del settore che permette la realizzazione di blocchi di progetto con 10 milioni di istanze e oltre. L’accelerazione multi-scenario su tutto il flusso accelera il tempo di sviluppo anche attraverso un numero sempre maggiore di scenari multi-mode e multi-corner.

Oltre a fornire risultati PPA al vertice e tempi di risposta ottimizzati, il sistema di implementazione Innovus offre un’interfaccia utente comune (UI) per tool di sintesi, implementazione e signoff. A questo si affianca l’integrazione a livello di modelli dati e di API con le soluzioni Tempus Timing Signoff e Quantus QRC Extraction. Insieme, questi ambienti garantiscono una convergenza di signoff veloce, accurata e pronta per i 10nm, cui si associa un flusso completamente personalizzabile. I clienti possono inoltre beneficiare di un robusto sistema di visualizzazione e reporting che potenzia le capacità di debugging, di analisi delle cause e di gestione del flusso di progettazione metrics-driven.

pb

Contenuti correlati

-

L’evoluzione dei System on chip

L’interesse per lo sviluppo dei SoC è sempre maggiore e la crescita del mercato di questo tipo di componenti evidenzia l’apprezzamento dei produttori di chip per un’architettura versatile e competitiva Leggi l’articolo completo su EO 521

-

I DSP Tensilica di Cadence per l’audio di NXP

I DSP Tensilica HiFi 5 di Cadence sono diventati un componente chiave nell’ultima famiglia di DSP audio per autoveicoli di NXP Semiconductors, consentendo di implementare funzionalità audio avanzate per veicoli software-defined di nuova generazione. NXP ha infatti...

-

I Soc wireless di Silicon Labs con funzionalità di energy harvesting

Silicon Labs ha realizzato la nuova famiglia di SoC wireless xG22E, espressamente concepita per operare con consumi ridottissimi, come richiesto dalle applicazioni di energy harvesting che non prevedono l’uso di batterie. La nuova linea è composta dai...

-

SoC wireless per dispositivi medicali connessi

La famiglia di dispositivi wireless sicuri e a basso consumo di Silicon Labs, come quelli della serie BG27, grazie alle loro caratteristiche rappresentano la soluzione ideale per applicazioni IoMT (Internet of Medical Things) Leggi l’articolo completo su...

-

Gestione termica nei sistemi elettronici: le basi fondamentali

In questo articolo vengono analizzate le potenziali fonti di calore all’interno di un’applicazione elettronica e illustrati vari metodi di gestione termica Leggi l’articolo completo su EO 514

-

La roadmap per SoC e MCU automotive di nuova generazione di Renesas

Renesas Electronics ha delineato i piani per SoC e microcontrollori (MCU) destinati a tutte le principali applicazioni automotive. L’azienda infatti ha fornito le anticipazioni sul suo SoC R-Car di quinta generazione per applicazioni ad alte prestazioni che...

-

Cadence espande la licenza di Pfizer al software di molecular design

Cadence Molecular Sciences (OpenEye), una business unit di Cadence, ha annunciato che Pfizer ha firmato un accordo per estendere ed espandere l’accesso ai prodotti Cadence e ai kit di strumenti di programmazione per la progettazione molecolare avanzata....

-

Cadence semplifica la progettazione da nodo a nodo e la migrazione del layout

Cadence Design Systems ha reso disponibile un flusso certificato di migrazione di progetto da nodo a nodo basato sul nuovo ambiente Cadence Virtuoso Studio alimentato da AI generativa. Il flusso è compatibile con i nodi avanzati di...

-

Silicon Labs ha presentato il SoC dual band FG28 con AI

Il nuovo SoC dual-band FG28 di Silicon Labs è stato progettato per reti e protocolli a lungo raggio come Amazon Sidewalk, Wi-SUN e altri protocolli proprietari. Si tratta di un componente che integra le interfacce radio sub-Gigahertz...

-

Proteggere l’IoT con i SoC e FPGA PolarFire

La protezione dei dispositivi IoT non dovrebbe riguardare semplicemente la protezione da edge a cloud, ma dovrebbe anche riguardare la protezione dell’intera catena di approvvigionamento coinvolta nella realizzazione di questi prodotti Leggi l’articolo completo su EO 510