ANALOG/MIXED SIGNAL

Clock IC

29

- ELETTRONICA OGGI 452 - MARZO 2016

HCSL o LVPECL) o come due uscite

single-ended (LVCMOS).

Grazie a Timing Commander è pos-

sibile eseguire la programmazione

in-system del componente via I2C

all’accensione e bypassare la confi-

gurazione memorizzata nella OTP, se

necessario, per soddisfare eventuali

modifiche apportate a livello di speci-

fiche o di prodotto. L’utente finale può

anche impostare parametri di disper-

sione dello spettro indipendenti per

applicazioni che adottano tale tecnica

per la riduzione delle interferenze elet-

tromagnetiche.

La famiglia VersaClock 5 di IDT affron-

ta e risolve delle problematiche chiave

dei generatori di clock. La combinazio-

ne tra molteplici uscite, un jitter estre-

mamente contenuto e rumore di fase e

consumo di potenza ridotti con la pro-

grammabilità comporta vantaggi tan-

gibili per i progettisti e gli utilizzatori

del prodotto. Grazie a essa è possibile

accelerare il ciclo di progetto e sempli-

ficare le fasi di sviluppo e validazione

come la ricerca degli errori e i test dei

margini.

Inoltre, il problema di approvvigiona-

mento dei quarzi viene ridotto, miglio-

rando al contempo l’affidabilità grazie

ad un minore numero di componenti

richiesti. Lo spazio occupato sulla

scheda, la BOM e il costo vengono ri-

dotti.

Componenti diversi

per soddisfare svariate esigenze

I

componenti

della

famiglia

IDT5P49V59XX VersaClock 5 si dif-

ferenziano leggermente in termini di

funzionalità, configurazioni e specifiche. Per analizzare le

potenzialità e la versatilità del componenti di questa famiglia

si prenda ad esempio il mod. IDT5P49V5925. Questo compo-

nente offre un clock LVCMOS di riferimento a 25 MHz buf-

ferizzato, oltre a quattro uscite indipendenti funzionanti nel

range da 1 MHz a 200 MHz. Queste uscite hanno uscite pro-

grammabili singolarmente (1,8V, 2,5V e 3,3V), abilitazione

delle uscite, controllo dello slew rate e funzionalità spread-

spectrum. Il rumore di fase e il jitter rms integrato sono in-

feriore a 0,7 picosecondi (610 femtosecondi per l’esattezza),

compreso il cross-talk interno, come mostrato nel grafico

dello spettro di questa uscita misurato con un analizzatore

di segnali (Fig. 5).

A causa delle frequenze elevate e del jitter molto contenuto,

non è semplice simulare il comportamento di questi compo-

nenti o misurarne le prestazioni. Di conseguenza, IDT for-

nisce i modelli IBIS. In aggiunta, sono disponibili schede di

valutazione per tutti i membri della famiglia per semplificare

il lavoro del progettista, in particolare quando impiegate in-

sieme alla piattaforma software Timing Commander (Fig. 6).

J

itter

:

un termine semplice

per un comportamento complesso

Non si può parlare di segnali di clock senza prendere in considerazione il jitter, un parame-

tro che ogni sistema con un clock ad alta frequenza e ne limitano le massime prestazioni

raggiungibili. Nel dominio del tempo, il jitter appare come uno sfasamento continuo at-

torno alla forma d’onda ideale, mentre nel dominio della frequenza è descritto da compo-

nenti spurie che si aggiungono al picco della frequenza fondamentale. Le indicazioni nei

domini del tempo e della frequenza sono perfettamente equivalenti e l’adozione di uno o

dell’altro dominio dipende dall’applicazione.

Il jitter è un argomento complesso, la sua presenza è dovuta a molteplici sorgenti e ha un

impatto sull’intero sistema. Può essere causato da imperfezioni del generatore di clock (ti-

picamente un quarzo o un clock esterno di riferimento) o degli oscillatori ad esso collegati,

dal rumore di fase, da altre sorgenti di rumore esterne, dall’accoppiamento sul circuito

stampato e dalle interferenze elettromagnetiche. Poiché esistono molti tipi di jitter, esso

può essere indicato con diverse unità di misura, come illustrato in tabella 1 insieme ai pa-

rametri principali che lo caratterizzano come il valormedio, il valore rms o il valore di picco.

Nei sistemi moderni ad alta velocità e larga banda, il jitter viene normalmente misurato in

picosecondi o millesimi di unità di periodo (UI).

Il jitter costituisce uno dei fattori principali che introducono non idealità nei sistemi, come

errori di temporizzazione nel campionamento delle radio definite dal software (SDR) o un

aumentodel tassodi errori (BER) prodottodall’interferenza tra simboli e dalla conseguente

chiusura del diagramma ad occhio nella trasmissione dati. I dettagli circa i tipi di jitter, le

loro sorgenti e i parametri che li caratterizzano sono discussi in tutorial dettagliati, come

AN-815 “Understanding Jitter Units “ e AN-827, “Application Relevance of Clock Jitter”.

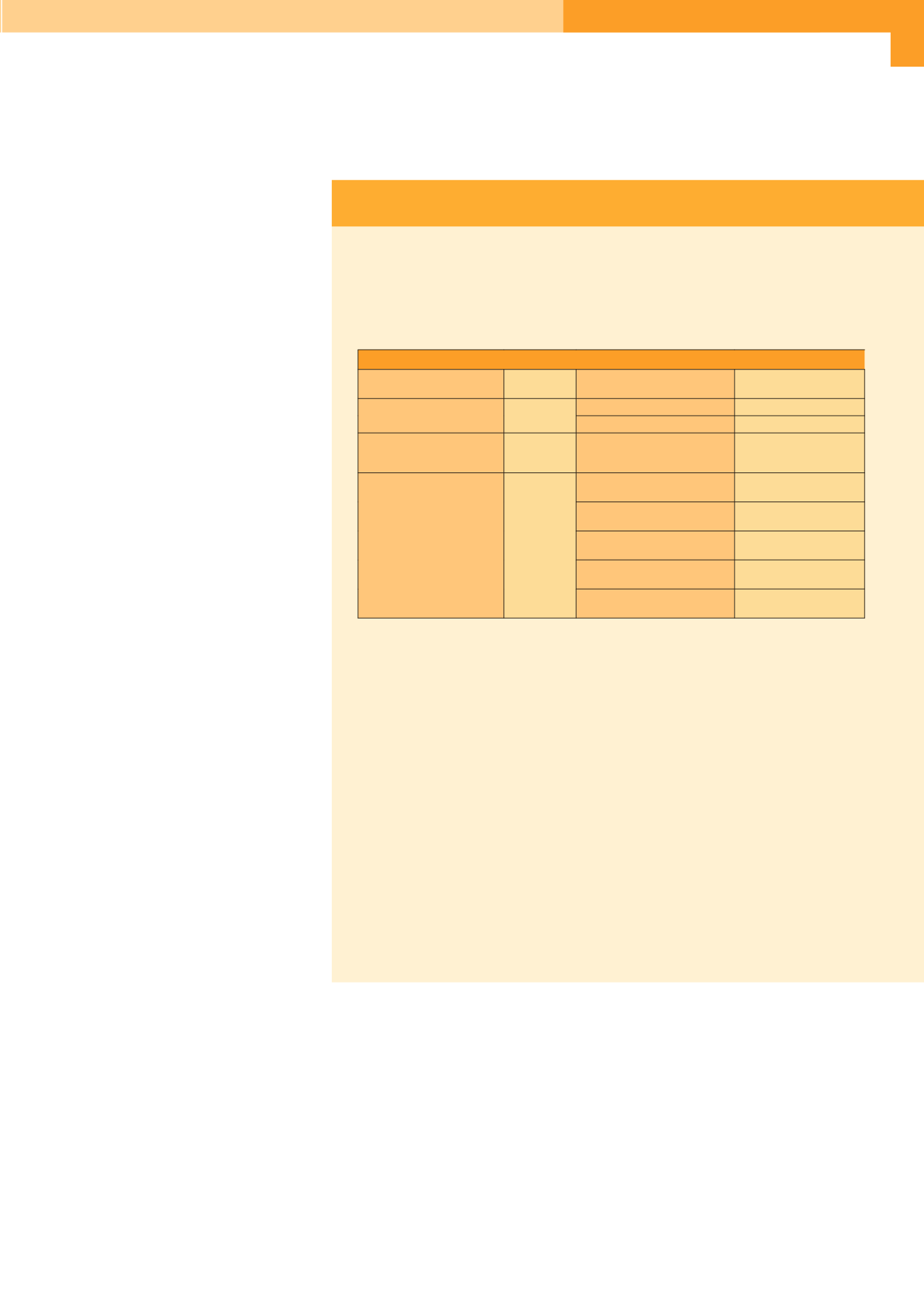

Tabella 1 – Esempi di vari tipi di jitter in funzione dell’applicazione

Application

(examples)

Relevant

Jiitter

Specification

(units)

Qualifier

Synchronous Interface

Synchronous Logi

c

Period

Jiiter

Pk-Pk Period Jiiter (time)

Bit Error Rate

RMS Period Jiiter (time)

10K cycles

Micro Complex

Motherboard Design

Spread Spectrum

High

Freq Jiiter

C2C Jiiter (time)

1K consecutive cycles

High Speed SerDes

ADC (RF Signal Chain)

Frequency

Domain Jiiter

Phase Noise, PN Plot (dBc/Hz)

(Frequency Domain Measurement)

Carrier Offset Freq

RMS Phase Jiiter (time)

(extrapolated from a PN Plot)

Integration band (i.e. fileter)

Pk-Pk Total Jiiter UI (time)

(SerDes Eye Closure Specification)

Random Jiiter Budget,

Integration Band (i.e. filter)

Spurs (dBc)

(Deterministic Jiiter)

Carrier Offset Freq

“Additive” RMS Phase Jiiter (time)

(Fan Out Buffer “relevance”)

Integration Band (i.e. filter)