ANALOG/MIXED SIGNAL

Clock IC

28

- ELETTRONICA OGGI 452 - MARZO 2016

3.0, ed Ethernet 1/10 Gigabit. Tuttavia, nonostante queste

elevate prestazioni di jitter e relative specifiche, non vi sono

penalizzazioni in termini di potenza dissipata. Infatti, questi

componenti richiedono una corrente del core di solo 100 mA

(a 3,3V), la metà di quella richiesta da analoghi dispositivi

presenti sul mercato, con un consumo complessivo inferiore

a 300 mW con tutte le uscite attive.

Vantaggi applicativi

I prodotti della serie VersaClock sono già stati utilizzati per

la realizzazione di vari prodotti di fascia alta, come il router

ISR860 di

Cisco .Questo prodotto di massa (circa un milio-

ne di pezzi all’anno) richiedeva molteplici segnali di clock

che dovevano essere pro-

grammabili per gestire ri-

chieste locali insieme alle

specifiche di altri mercati.

I progettisti di Cisco hanno

impiegato questo compo-

nente compatto e a bas-

sa potenza con un’uscita

programmata per i livelli

CMOS, per minimizzare le

interferenze con le schede

interne compatibili con i

segnali radio 4G. Le altre

uscite sono programmate

con livelli LVDS, LVPECL e

HCSL. Altri parametri pro-

grammati includono l’in-

tensità del segnale di usci-

ta, per adattarsi a varie

impostazioni relative alle

interferenze elettromagnetiche. Il dispositivo consente l’ese-

cuzione di modifiche delle configurazioni in meno di un’ora,

mentre le unità programmate in fabbrica si adattano alle esi-

genze della produzione in volumi.

Programmabilità semplificata

Tradizionalmente, un compromesso meno “appareiscente” tra

programmabilità e flessibilità di configurazione era costituito

dalla difficolta di effettuare efficacemente le configurazioni

desiderate. Questo problema è stato superato con il Timing

Commander di IDT per la famiglia VersaClock (Fig. 4). La sua

interfaccia grafica intuitiva e flessibile consente agli utenti

di programmare facilmente i quattro divisori frazionari del-

le uscite per produrre quattro frequenze indipendenti con

un errore di 0 ppm. Essa Consente inoltre di impostare ogni

coppia di uscite universali come coppia differenziale (LVDS,

Fig. 6 – IDT mette a disposizione schede di valutazione per tutti i mem-

bri della famiglia di generatori di clock VersaClock 5

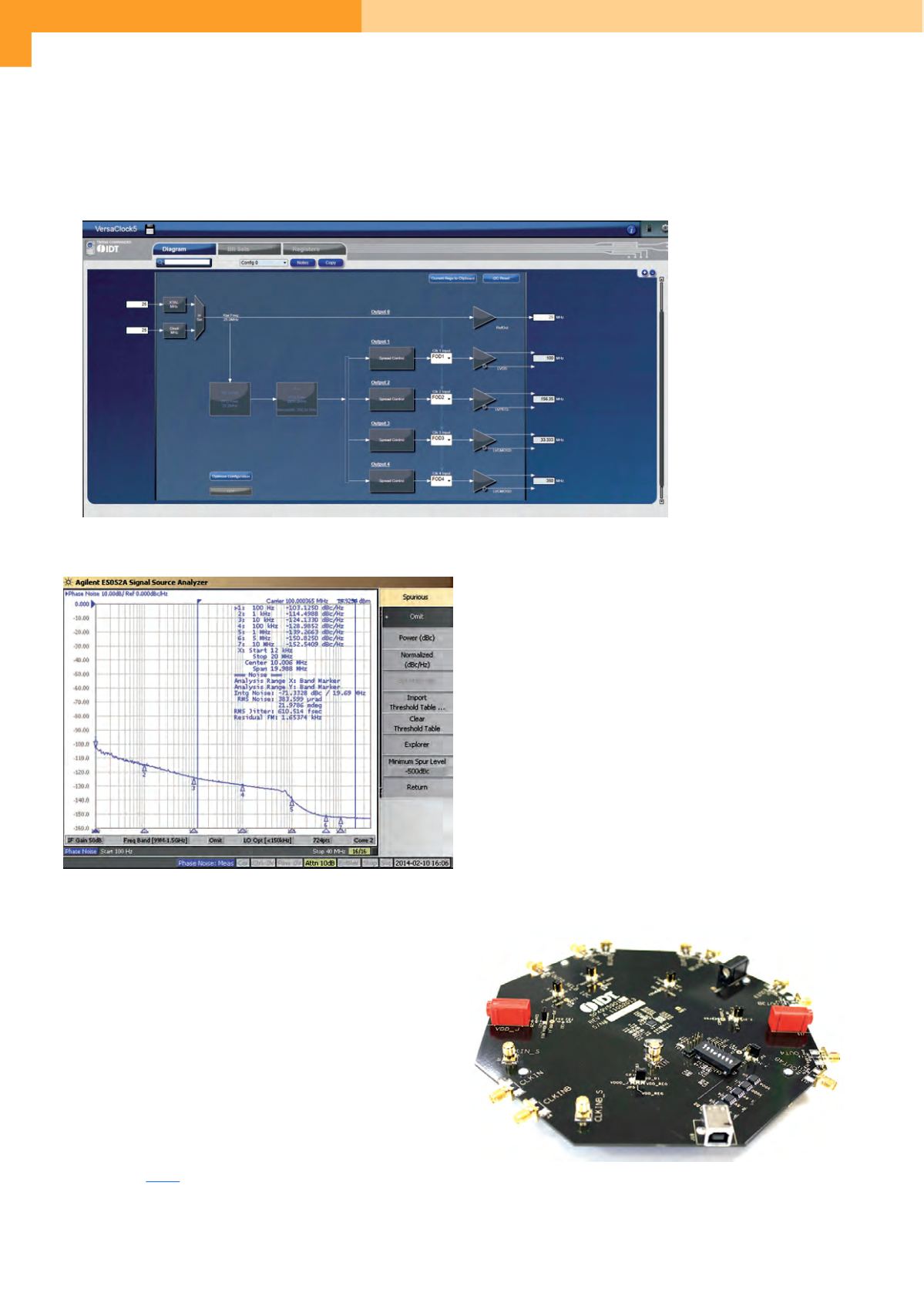

Fig. 4 – Per semplificare la programmazione IDT mette a disposizione la GUI Timing Commander per la famiglia

VersaClock

Fig. 5 – Schermata dell’analizzatore di segnale relativo al rumore di fase

e al relativo jitter