ANALOG/MIXED SIGNAL

Clock IC

26

- ELETTRONICA OGGI 452 - MARZO 2016

I vantaggi dei generatori

di clock programmabili

L

a stragrande maggioranza dei circuiti elettronici

dipende da un segnale di clock, che può essere

considerato come il “battito cardiaco” dei processori.

Tuttavia, diversamente dagli organismi viventi, la maggior

parte dei progetti moderni richiede più di una singola fre-

quenza di clock. Un router, una console di gioco, uno stru-

mento di misura o un ricevitore satellitare portatile possono

richiedere quattro, sei o più segnali di clock indipendenti,

per soddisfare le richieste di processore, interfacce e peri-

feriche di rete, spesso caratterizzati da segnali con proprietà

e formati differenti.

Fornire questi clock multipli rappresenta una sfida significa-

tiva per i progettisti, impegnati nel contempo a minimizzare

il consumo di potenza, le dimensioni delle schede ed i costi,

senza sacrificare le prestazioni elevate richieste delle appli-

cazioni e dai relativi standard tecnologici. La soluzione più

ovvia è il ricorso a un generatore di clock con relativo quarzo

per ogni frequenza richiesta. Questo approccio non solo è

costoso in termini di potenza, spazio e costi, ma complica la

Bom in quanto è necessario ricorrere a più circuiti integrati,

spesso di produttori differenti.

Esiste un approccio alternativo: impiegare un singolo circuito

integrato che genera segnali di clock indipendenti a frequen-

ze fisse, a partire da un’unica sorgente. Ciò riduce natural-

mente il numero di quarzi e di circuiti integrati richiesti. An-

che se questa potrebbe apparire la soluzione ideale, in realtà,

le prestazioni che si ottengono sono spesso inadeguate e la

flessibilità è estremamente ridotta. Una soluzione più idonea

è l’utilizzo di un generatore di clock programmabile multi-

uscita. A seconda del tipo di progetto, le frequenze di uscita

sono programmate in fabbrica o dall’utente, garantendo così

notevole flessibilità e semplificazione della lista componenti

anche quando si realizzano più versioni di un prodotto.

Potrebbe sembrare che i problemi legati alla necessità di

molteplici segnali di clock siano risolti con l’adozione di que-

sti circuiti integrati, ma non è così. Innanzitutto, a causa della

loro architettura interna, questi chip generano errori nel va-

lore della frequenza iniziale, inammissibili in molte applica-

zioni. Inoltre si manifestano fenomeni di diafonia (cross-talk)

tra le varie uscite, che portano alla generazione di compo-

nenti spurie in frequenza che possono deteriorare il funzio-

namento del sistema.

Oltre a questi limiti prestazionali fondamentali, la maggior

parte dei circuiti integrati multi-uscita mancano della flessi-

bilità necessaria per regolare altri parametri critici che de-

vono essere adattati ai circuiti che pilotano. Tra questi para-

metri si possono annoverare la velocità dei fronti (slew rate)

del segnale di clock, le caratteristiche di dispersione dello

spettro (spread-spectrum) e la configurazione delle uscite

(tipo LVDS, LVCMOS, LVPECL). Inoltre, sebbene le frequenze

di lavoro siano inizialmente programmabili, non tutti i model-

li consentono di riprogrammare le frequenze per adattarsi

a specifiche e applicazioni diverse. Conseguentemente, la

maggior parte dei generatori di clock programmabili non

rappresentano in molti una soluzione del tutto soddisfacente.

Senza dimenticare che questi circuiti integrati evidenziano

Baljit Chandhoke

Product Line manager

IDT

Grazie a componenti di questo tipo è

possibile ridurre il numero di componenti

richiesto e ottenere il miglior compromesso

tra potenza dissipata e jitter

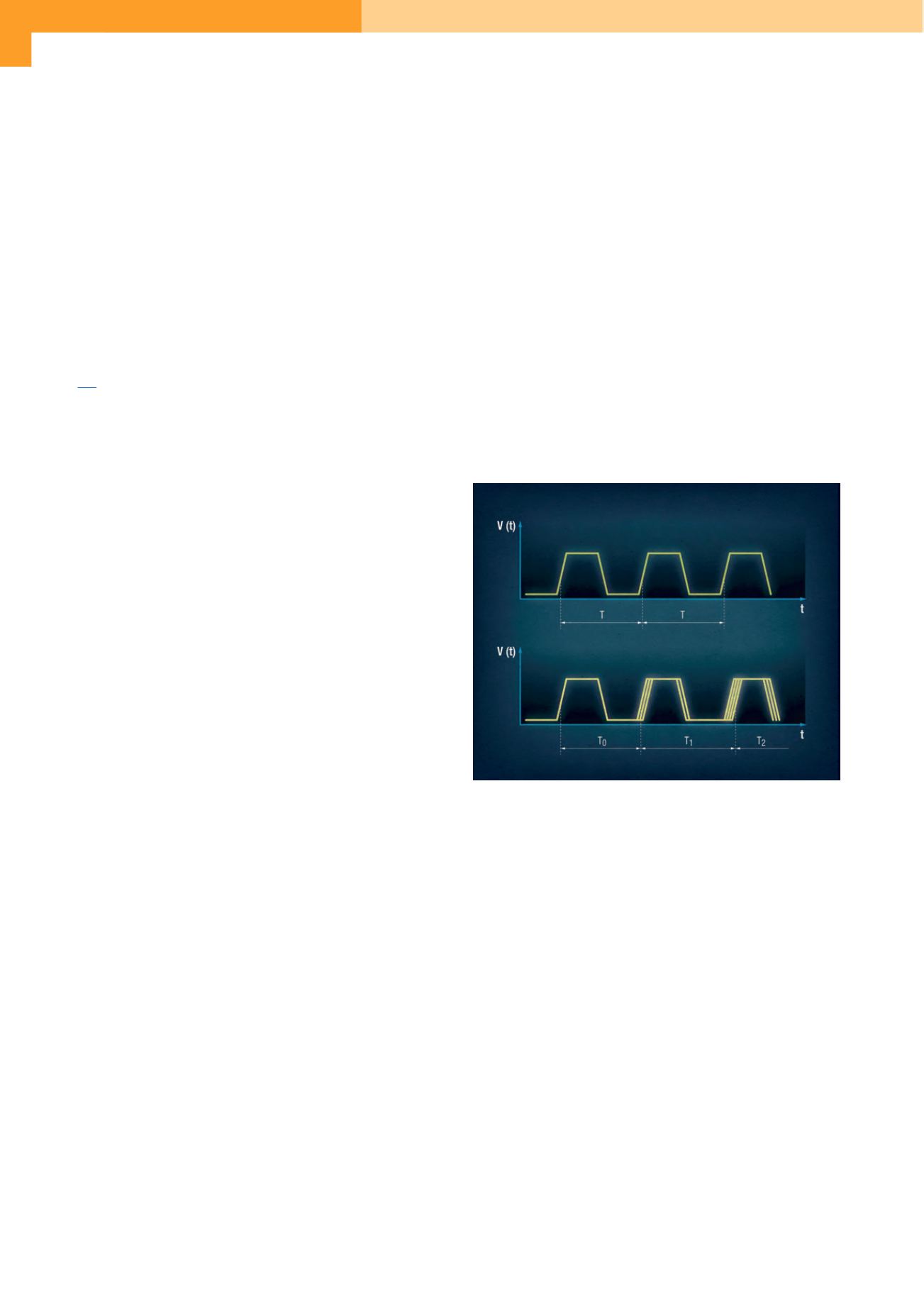

Fig. 1 – Il jitter nel dominio del tempo