27

- ELETTRONICA OGGI 452 - MARZO 2016

ANALOG/MIXED SIGNAL

Clock IC

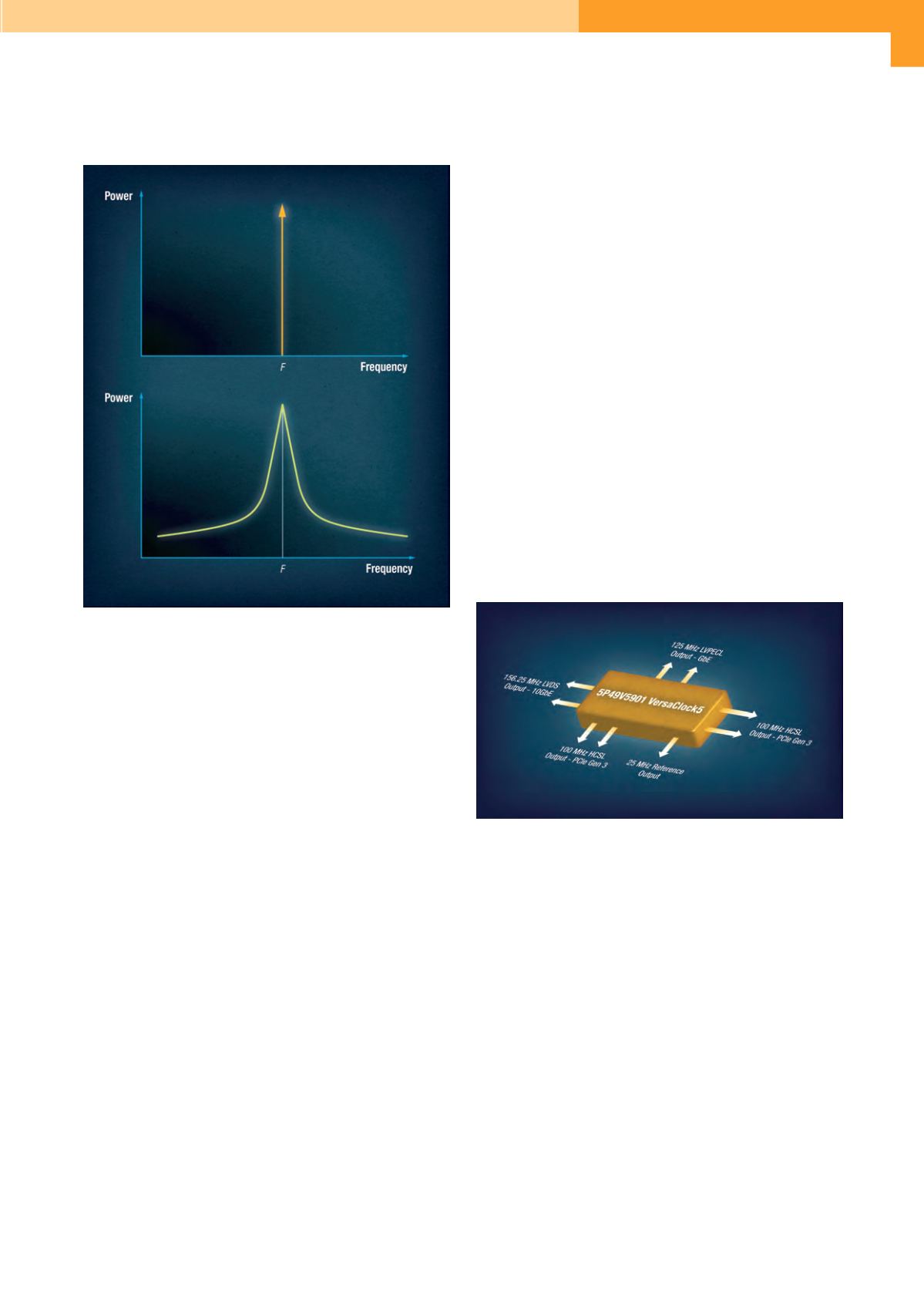

carenze in termini di jitter, una delle specifiche più impor-

tanti che caratterizzano la qualità del segnale di clock. Ogni

generatore reale produce un segnale di clock con picco-

le variazioni attorno alla frequenza nominale. Nel dominio

del tempo (Fig. 1) tali variazioni appaiono come salti avanti

e indietro lungo l’asse temporale, mentre nel dominio della

frequenza si manifestano come componenti spurie indeside-

rate nello spettro (Fig. 2).

Il jitter è un fenomeno complesso che assume diverse forme,

ha molte origini e può essere caratterizzato in molti modi. La

quantità massima e il tipo di jitter tollerabile da un sistema

sono legati all’applicazione specifica, agli obiettivi prestazio-

nali e, in molti casi, agli standard applicabili.

Come per molte non idealità, esistono modi per minimizzare

il problema del jitter, con ovviamente un prezzo da pagare. I

progettisti di circuiti integrati più esperti possono ridurre il

jitter in cambio però di un incremento del consumo di poten-

za. A questo punto è utile vedere se è possibile individuare

un compromesso tra questi parametri.

Componenti ottimizzati

Nonostante gli svantaggi appena discussi, i vantaggi po-

tenziali offerti dai generatori di clock programmabili multi-

uscita sono evidenti. Per questo motivo i produttori di cir-

cuiti integrati hanno focalizzato i loro sforzi per risolvere il

problema e le più recenti famiglie di questi generatori pro-

grammabili hanno superato molti degli svantaggi menzio-

nati. Un esempio significativo è la famiglia di generatori di

clock programmabili VersaClock 5 di IDT, giunti alla quinta

generazione (Fig. 3).

Questi generatori di clock programmabili a bassa potenza

abbinano elevate prestazioni di jitter e flessibilità, a uscite

universali, capaci di generare frequenze di clock in un am-

pio spettro. Ogni componente di questa serie può generare

quattro segnali di clock indipendenti con un errore di set-up

pari a 0 ppm, a partire da un singolo clock di riferimento o

da un quarzo esterno. Le frequenze di clock sono program-

mabili sul campo attraverso un’interfaccia I

2

C o tramite il

software Timing Commander di IDT. L’intervallo di frequenze

di uscita va da 1 MHz a 350 MHz in modalità di uscita diffe-

renziale (LVDS, LVPECL, HCSL) e fino a 200 MHz in modalità

single-ended (LVCMOS). I package disponibili sono di tipo

VFQFPN e vanno dal modello a 24 piedini (4x4mm) fino alla

versione a 48 piedini.

Ogni dispositivo, inoltre, può memorizzare quattro diverse

configurazioni in una memoria non volatile OTP e le confi-

gurazioni sono selezionabili utilizzando i GPIO del proces-

sore o cablata attraverso due pin di selezione presenti sul

componente. Le varie configurazioni salvate possono essere

usate per diverse modalità operative (funzionamento com-

pleto o parziale, spegnimento parziale), per adattarsi a stan-

dard regionali (USA, Giappone o Europa) o per quantificare

i margini di corretto funzionamento durante il collaudo in

produzione.

Tuttavia, le caratteristiche funzionali costituiscono solo un

aspetto in quanto l’elemento cruciale è rappresentato dalle

prestazioni. Infatti, le funzionalità sono importanti a patto che

le prestazioni del dispositivo siano in grado di soddisfare le

specifiche più elevate. I dispositivi della serie VersaClock 5

hanno un jitter di fase inferiore a 0,7 ps (rms) da 12 kHz

a 20 MHz e rispettano le specifiche di clock più stringen-

ti imposte da standard come PCIe generazioni 1/2/3, USB

Fig. 3 – La famiglia VersaClock 5 di IDT è formata da generatori di clock

di quinta generazione in grado di generare quattro clock indipendenti

Fig. 2 – Il jitter nel dominio della frequenza