34

- ELETTRONICA OGGI 452 - MARZO 2016

a tendenza che sembra accanirsi da qualche

anno su progettisti e costruttori non si limita al

passaggio dai Single Core ai Multi Core ma ha ormai

coinvolto gli Heterogeneous Core che di questi tem-

pi sono chiamati anche Chip MultiProcessor (CMP),

Multi Processing SoC (MPSoC), Many Core, Massive-

ly Multi Core e persino Various Multi Core anche se

il significato è evidentemente lo stesso perché con-

siste nel mettere sullo stesso die core con diverse

caratteristiche hardware e software e persino con

funzionalità specifiche non solo a livello fisico bensì

pure a livello di proprietà intellettuale.

L’OpenCL, o Open Computing Language, costituisce

una piattaforma di programmazione basata sul lin-

guaggio C che consente di amalgamare nello stesso

silicio core CPU, GPU, DSP e FPGA in moduli funzi-

onali distinti. Il fattore chiave che consente questa

nuovo paradigma nella programmazione a livello di

sistema è il partizionamento delle temporizzazioni

fra i core simmetrici SMP, Symmetric MultiProcess-

ing, e i core asimmetrici AMP, Asymmetric MultiPro-

cessing, perché solo così è possibile far convivere

core con esigenze applicative che possono essere

molto diverse. Basti pensare che un DSP deve per

sua natura ignorare per quanto possibile gli inter-

rupt per poter reiterare indefinitamente i cicli di

elaborazione sulle lunghe sequenze di simboli che

rappresentano i segnali audio o video e perciò la-

vorare senza interruzioni per garantire un’usci-

ta sincronizzata in tempo reale con l’acquisizione.

D’altro canto, implementando algoritmi con un el-

evato Instruction-Level Parallelism (ILP) si ottiene

un sofisticato livello di partizione delle risorse che

permette di far convivere due o più sistemi oper-

ativi di diverso tipo e cioè general-purpose, GPOS,

e in tempo reale, RTOS, limitatamente ad alcuni dei

core installati. I due OS hanno esigenze diverse per-

ché i GP devono occuparsi di un maggior numero di

attività offrendo un’elaborazione composita da più

funzionalità e perciò devono avere procedure di ac-

cesso alle periferiche più sofisticate mentre gli RT

agiscono sull’hardware a basso livello per accedere

a risorse limitate ma in grado di generare un’effi-

cace elaborazione in tempo reale. L’asimmetria del-

le temporizzazioni a livello hardware assume così

un significato nella differenziazione delle risorse

software e viceversa.

Per le sue caratteristiche di versatilità il linguaggio

OpenCL diventa fondamentale per l’elaborazione

eterogenea e per la riutilizzabilità delle funzioni sul

silicio soprattutto grazie al Device Partitioning intro-

dotto nella versione OpenCL 1.2 e alla possibilità di

gestire le Shared Virtual Memory introdotta nelle

versioni OpenCL 2.x. In pratica, le comunicazioni fra

le diverse unità avvengono a un metalivello che è in

effetti una memoria virtuale opportunamente gestita

in modo da assegnare in successione sequenziale

la temporizzazione a tutti gli eventi sincronizzando

le attività. Di conseguenza, si ottiene un parallelis-

mo scalabile globalmente asincrono ma sincrono

TECH-FOCUS

NEW COMPUTING

Il passo evolutivo che segue dopo l’integrazione di più core nello stesso

silicio è la loro differenziazione funzionale per creare processori capaci di

svolgere in parallelo le mansioni di CPU, DSP, GPU e persino Cpld o Fpga

L

Gianluca Scotti

PROCESSORI ETEROGENEI

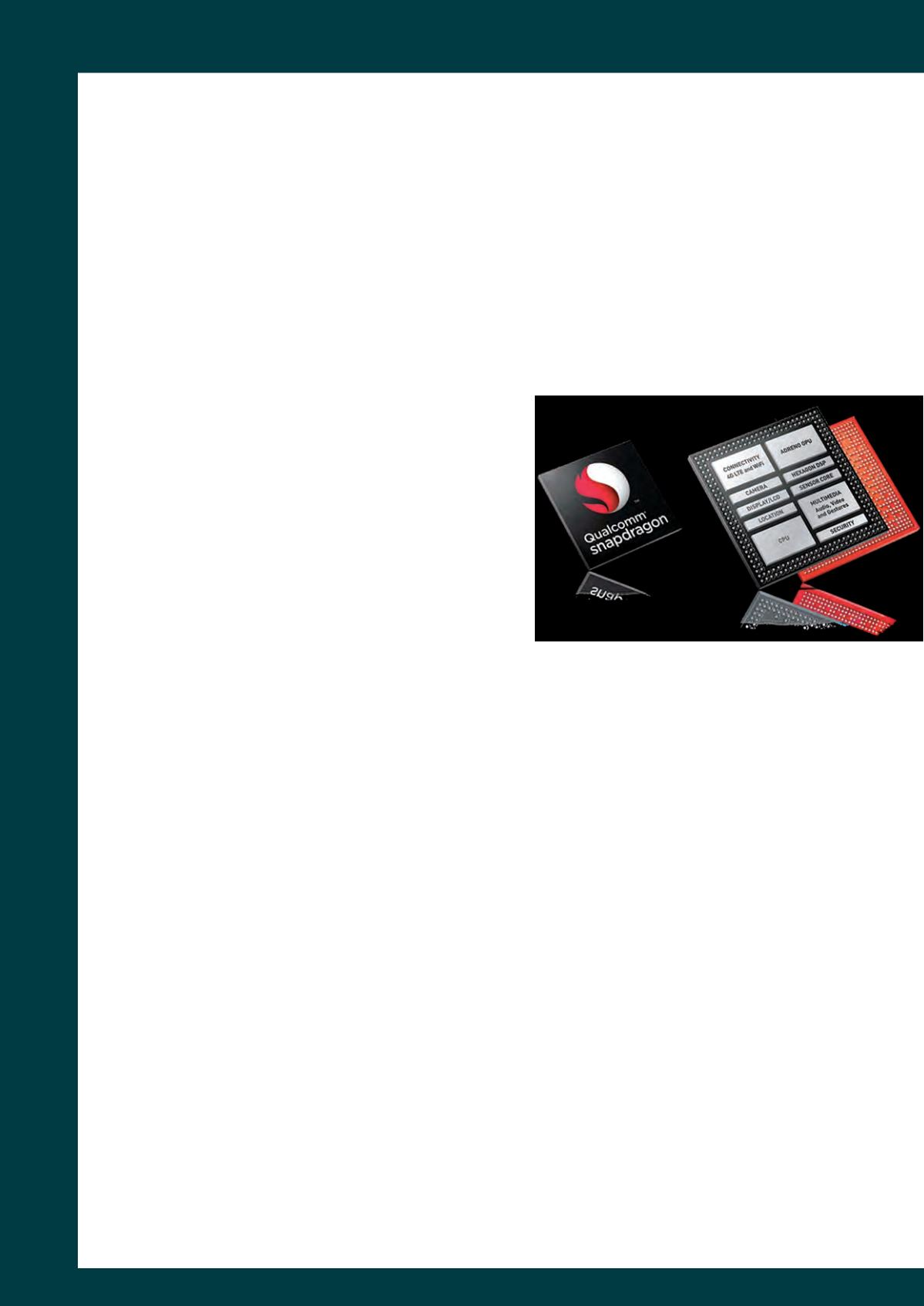

Fig. 1 – L’all-in-one SoC Qualcomm Snapdragon 820 integra in

geometria di riga da 14 nm l’innovativa CPU quad-core Kryo a 64

bit insieme al DSP Hexagon 680 e alla GPU Adreno 530 grazie a una

gestione delle temporizzazioni “sinfonica”