DIGITAL

DDC

52

- ELETTRONICA OGGI 450 - NOVEMBRE/DICEMBRE 2015

durrebbe la quantità di dati di uscita in banda di

un fattore 8.

Questa minore velocità di trasmissione dati ridu-

ce la complessità dello schema circuitale del si-

stema, riducendo il numero di canali JESD204B di

uscita dell’ADC. La riduzione della banda in uscita

dell’ADC contribuisce allo sviluppo di progetti più

compatti. Ad esempio, nel caso in cui la potenza e

le dimensioni del sistema consentono l’uso di un

solo FPGA sulla scheda, il numero di transceiver

seriali ad alta velocità supportati può limitare il

numero di ADC senza l’uso di conversioni DDC.

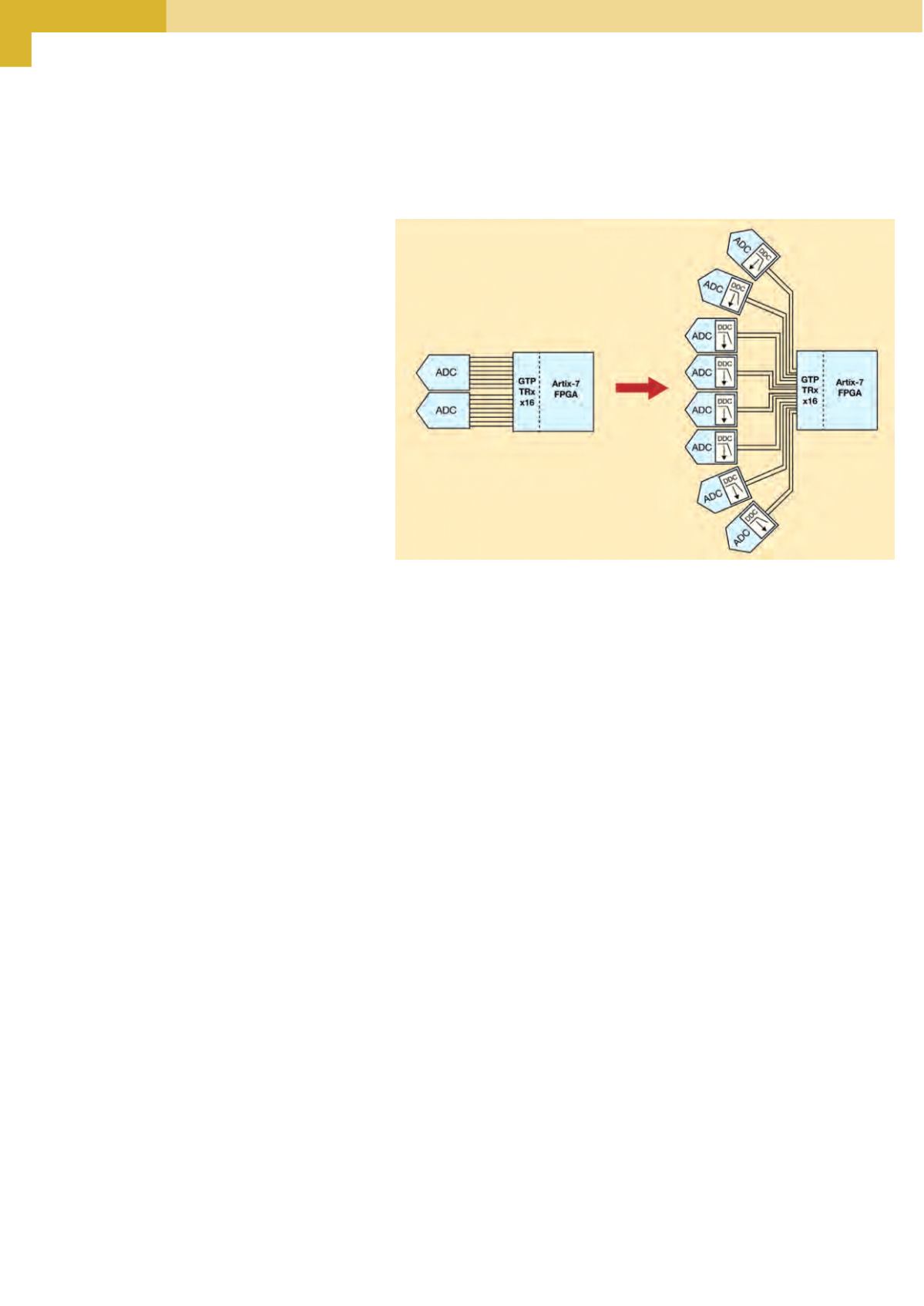

Nel caso in cui il sistema richieda una banda ri-

stretta, la decimazione all’interno degli ADC aiuta

a rimuovere questa limitazione. L’uso di un singolo

blocco DDC di decimazione per 8 consente allo

stesso sistema basato su FPGA Artix 9 di Xilinx di

supportare un numero di ADC quattro volte supe-

riore riducendo la banda in uscita degli ADC ad

appena due canali dati in uscita. Per questo caso

particolare, sarebbe possibile utilizzare fino a otto

ADC con DDC assieme ai 16 transceiver GTP pre-

senti in un FPGA Artix 7 (Fig. 2).

L’impatto dei filtri DDC su SNR e SFDR?

Il prossimo aspetto da analizzare è la variazione delle pre-

stazioni analogiche del rapporto segnale-rumore (SNR) e

dell’intervallo dinamico libero da spurie (SFDR) quando i fil-

tri DDC sono in funzione o meno. Dato che il rumore in banda

del convertitore è filtrato e che si osserva solo uno spettro

ridotto, ci si può aspettare che la potenza del segnale rispetto

al rumore osservato sia superiore.

L’intervallo dinamico dell’ADC sarà migliore all’interno della

banda passante del filtro. Il miglior rapporto segnale/rumore

che si ottiene grazie alla DDC, è un vantaggio intrinseco della

decimazione e del filtraggio dello spettro in banda. Il filtrag-

gio digitale ad opera del DDC è usato per filtrare il rumore al

di fuori di una banda più ridotta. Il calcolo del rapporto SNR

dell’ADC deve quindi includere un fattore di correzione per

questo filtraggio che tiene conto del guadagno di elaborazio-

ne del rumore filtrato. Usando un filtro digitale perfetto, per

ogni riduzione di banda per un fattore di potenza di due, il

guadagno di elaborazione legato al rumore filtrato aumen-

terà di +3 dB:

SNR ideale (con guadagno di elaborazione) =

6.02*N + 1.76 dB + 10log10(fs/(2*BW))

Un chiaro vantaggio legato all’uso dei blocchi DDC è la ca-

pacità di far cadere le armoniche del segnale fondamen-

tale al di fuori della banda di interesse. Con un’opportuna

disposizione delle frequenze, il filtraggio digitale farà sì che

le armoniche non siano viste all’interno della stretta banda

del blocco DDC, con conseguente aumento delle prestazioni

SFDR del sistema. Nei sistemi in cui è necessaria solo una

banda stretta, un blocco DDC garantisce un guadagno di ela-

borazione dell’ADC, filtrando il rumore in banda. Ciò contri-

buisce ad aumentare il rapporto segnale/rumore osservato

all’interno della banda di interesse. Un ulteriore vantaggio è

che, con un’opportuna pianificazione delle frequenze, le ar-

moniche tipicamente dominanti di secondo e di terzo ordine

della fondamentale cadono al di fuori della banda regolata

di interesse e sono filtrate digitalmente. Questo aumenta il

SFDR del sistema.

Due ultimi aspetti restano da considerare: quello relativo alla

necessità di usare filtri esterni e quello relativo alla possibili-

tà di avere più DDC in un ADC.

Per quanto concerne il primo aspetto, è bene tener presente

che i convertitori ADC che usano blocchi DDC interni posso-

no avvalersi di filtri analogici aggiuntivi, come avverrebbe

normalmente in assenza di filtraggio DDC. Per applicazioni

in banda larga, i DDC consentono di alleggerire i vincoli di

filtraggio richiesto in ingresso all’ADC. Per quanto concer-

ne invece il secondo aspetto, è bene sapere che è possibile

avere più DDC all’interno di un ADC, ciascuno con un proprio

NCO che si regola su bande separate attraverso la regione di

Nyquist. Uno schema di questo tipo consente di osservare

più bande di frequenza e riassegnare risorse ad altri compito

come la canalizzazione di più ADC per sistemi FDM.

Fig. 2 – L’uso dei blocchi DDC con un fattore di decimazione di 8 consente agli stessi 16

transceiver GTP da 6,6 Gbps del dispositivo Artix 7 di Xilinx di supportare otto ADC con

dati I/Q decimati su due canali di interfaccia JESD204B ciascuno, anziché due ADC che

hanno in uscita la banda completa su otto canali