49

- ELETTRONICA OGGI 450 - NOVEMBRE/DICEMBRE 2015

DIGITAL

FPGA & PROCESSOR

struttura FPGA è possibile inserire i valori temporanei in una

complessa pipeline in grado di assicurare che gli elementi DSP

abbiano a disposizione i ogni momento i dati pertinenti.

Grazie alla struttura FPGA è possibile effettuare operazioni

che non sono eseguibili facilmente in una ALU standard. Ad

esempio, le funzioni di crittografia e molti algoritmi utilizzati

nella comunicazione digitale, come i decoder Viterbi e Turbo,

spesso utilizzano il modulo e altre elaborazioni aritmetiche

non standard.

Grazie alla possibilità di avere un completo controllo degli ele-

menti logici, una ALU custom basata su FGPA garantirà qua-

si sempre risultati migliori rispetto a un’emulazione software

eseguita su un core processore standard.

Lo standard OpenCL

L’arrivo di linguaggi come OpenCL (Open Computing Langua-

ge) molto probabilmente semplificherà la creazione di copro-

cessori che possono essere gestiti con la massima flessibilità

in funzione delle particolari esigenze dell’applicazione. Anche

se OpenCL è stato sviluppato in origine per mettere a disposi-

zione la potenza di calcolo delle unità di elaborazione grafica

(GPU) ai programmatori più abituati a lavorare con architetture

di uso generale come ARM o x86, aziende come Altera hanno

adottato OpenCL con l’obiettivo di semplificare la creazione di

engine di calcolo custom.

Le funzioni OpenCL prendono la forma di kernel di calcolo: in

altre parole loop di tipo vettoriale da utilizzare per elaborare

più elementi di dati in parallelo. OpenCL comprende un am-

biente runtime che carica i kernel e i rispettivi dati nei proces-

sori target, avvia l’esecuzione e quindi carica i risultati una

volta completati i calcoli. Gli strumenti di compilazione conver-

tono l’algoritmo in linguaggio OpenCL in un’implementazione

adatta per la configurazione all’interno di un FPGA.

Un altro modo di trasferire l’overhead software dal processore

all’ FPGA prevede la riduzione della frequenza degli interrupt.

Ogni interrupt richiede che il processore arresti qualunque

operazione in corso al fine di acquisire o di inviare alcuni dati

attraverso una porta I/O. Ogni interrupt sposta e registra i con-

tenuti nello stack, impegnando cicli di clock del processore.

L’engine di calcolo analogico (ACE) integrato nei dispositivi

della linea SmartFusion di Microsemi è un processore paral-

lelo indipendente che controlla la varie porte I/O analogiche

supportate dal dispositivo.

ACE è format da due engine: SSE (Sampling Sequencing Engi-

ne) e PPE (Post-Processing Engine). Il primo acquisisce i dati

da ingressi analogici e li trasferisce al secondo che può ese-

guire funzioni quali il filtraggio passa-basso per rimuovere il

rumore e trasformare i dati in un formato funzionale per il pro-

cessore. Il trasferimento di queste funzioni nell’hardware con-

tribuisce a ridurre notevolmente l’onere legato alla gestione

degli interrupt da parte del processore.

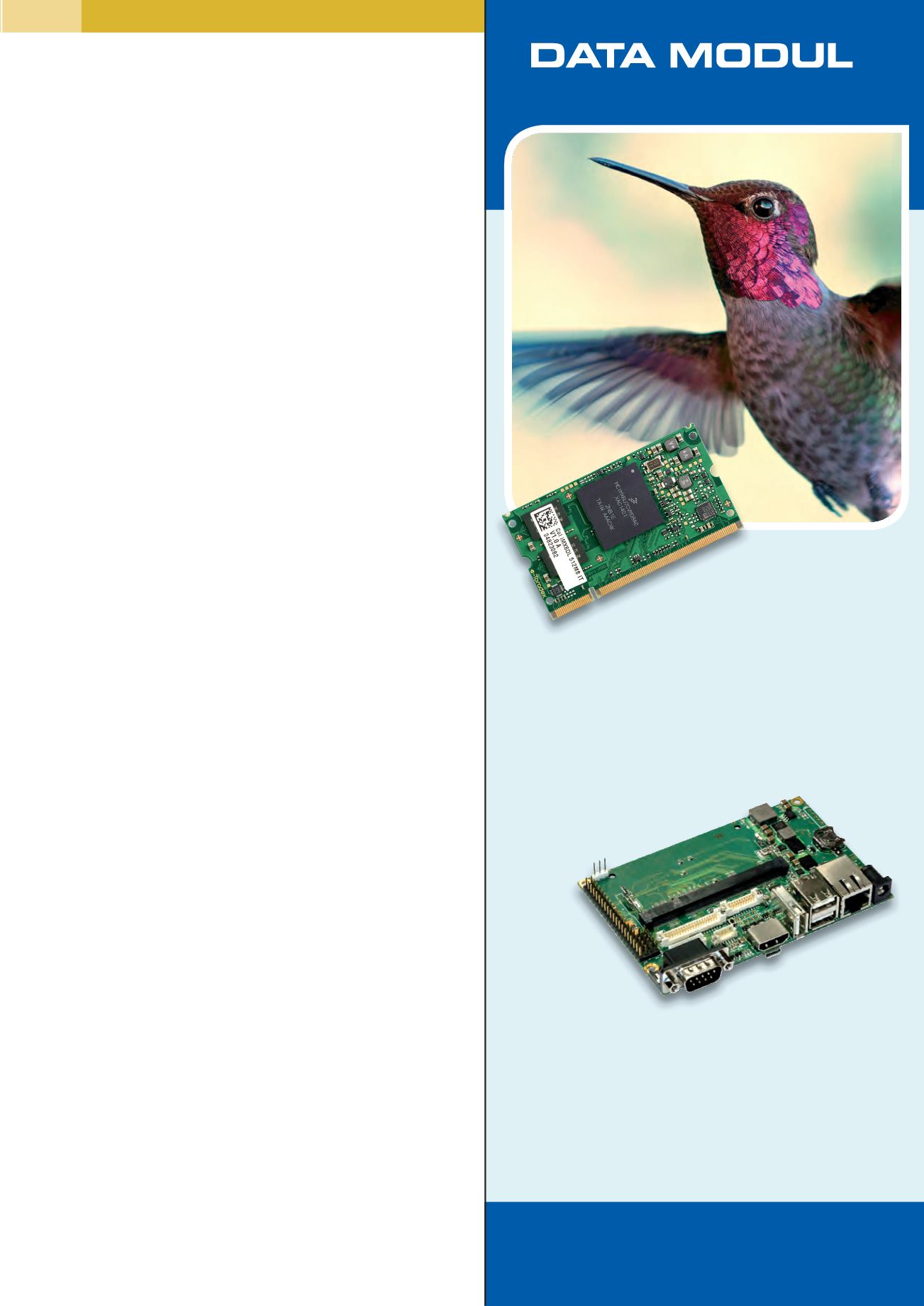

DATA MODUL Italia, S.r.l. Viale Cooperazione, 15 | 20095 Cusano Milanino - MI- Tel. +39-02-664 098 68 | italy@data-modul.com | www.data-modul.com » Freescale i.MX6 CPU (Solo/Dual Lite) » RAM 256MB/512MB, Flash 4GB eMMC » CAN, USB, ETH, UART, SPI, I²C e oltre » 24 bit RGB TTL fino a 1920x1200 Pixel » WinEC7/2013 e Supporto Linux OS » Baseboard per Toradex Colibri T20/T30/VF50/VF61/iMX6 » 2 x 24 Bit LVDS/TTL RGB » Alimentazione d’ingresso: +9 to +24V DC » Alimentazione scheda: 4.3” - 10.4” » RS232/485/422/CAN, ETH, µSD-Card, SPI, I²C, 4 x USB Colibri iMX6 eDM-CB-Colibri