DIGITAL

FPGA & PROCESSOR

47

- ELETTRONICA OGGI 450 - NOVEMBRE/DICEMBRE 2015

spositivo può rappresentare il nucleo centrale di un sistema

embedded completo. Questi dispositivi possono garantire le

prestazioni di processore, memoria e logica personalizzata

all’interno di un unico chip. Sebbene un processore cablato

in una struttura FPGA occupi meno spazio sul die, molti pro-

getti prevedono ora l’integrazione di uno o più core di pro-

cessore nella struttura logica programmabile per sfruttarne

la maggiore flessibilità.

Processori ARM

Negli ultimi anni, la maggior parte dei produttori di FPGA ha

adottato l’architettura ARM per i processori embedded ca-

blati.

Microsemiè stata la prima azienda a utilizzare questa

architettura con gli FPGA. L’architettura SmartFusion dell’a-

zienda prevede infatti l’abbinamento tra un core ARM Cortex-

M3 e una struttura FPGA non volatile basata su tecnologia

flash (Fig. 1). In questo modo le componenti hardware del si-

stema possono essere attivate non appena viene ripristinata

l’alimentazione, piuttosto che dover attendere che si conclu-

da la configurazione dell’FPGA da parte della memoria ROM

esterna.

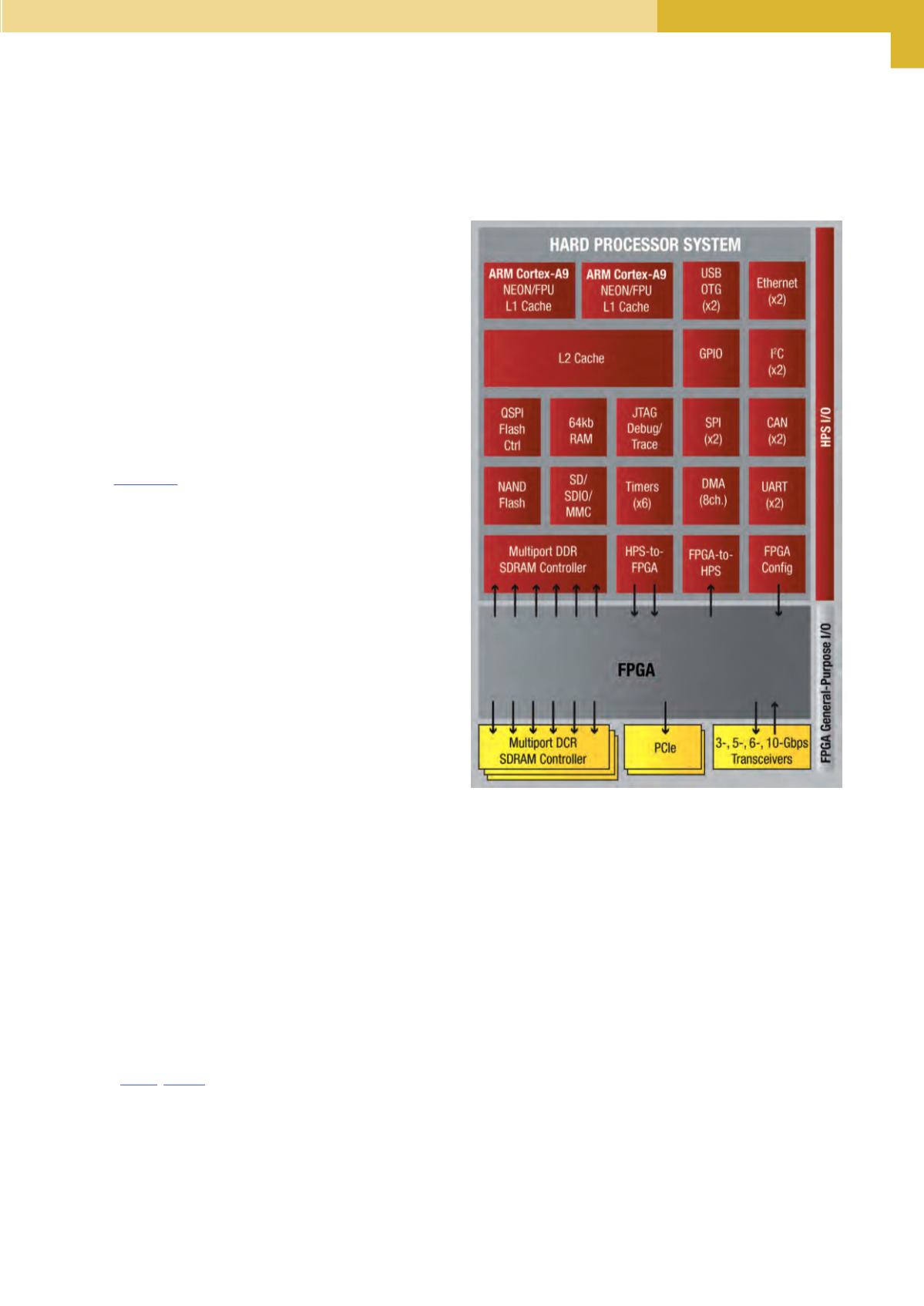

I core Cortex-A9, in grado di garantire le maggiori prestazio-

ni, sono i nuclei centrali di due famiglie di FPGA sviluppate

da Altera e Xilinx. I dispositivi SoC Cyclone di Altera e Zynq

di Xilinx integrano due processori ARM (Fig. 2), che consen-

tono di utilizzare tali dispositivi come engine di calcolo ad

alte prestazioni.

Oltre a utilizzare il core Cortex-M3 per i propri FPGA, Micro-

semi ha anche adottato una versione di MCU della serie M

(sempre di ARM) per le proprie logiche programmabili stan-

dard. Ottimizzato per l’implementazione all’interno di una

struttura FPGA, il core Cortex-M1 – versione semplificata del

core Cortex-M3 - è progettato in modo da non richiedere sul

die uno spazio superiore a quello necessario per un core

8051, pur essendo basato su una pipeline a 32 bit anziché

a 8 bit.

Come la versione M3, anche M1 esegue il set di istruzioni

Thumb2, ma con alcune istruzioni e funzionalità in meno. La

struttura degli interrupt M1 è stata semplificata per rispar-

miare spazio e supporta 32 fonti di interrupt rispetto alle 256

di M3.

La disponibilità di strumenti di sviluppo open-source ha con-

tribuito all’utilizzo di altri core con differenti architetture negli

FPGA.

Altera,

Latticee Xilinx hanno sviluppato le proprie ar-

chitetture di processore basate su una struttura di tipo RISC,

ciascuna delle quali è ottimizzata per l’utilizzo all’interno di

una struttura logica programmabile. Grazie alla disponibilità

di tool per la compilazione e il linking basati su Eclipse (un

ambiente quindi open source), i produttori di FPGA sempli-

ficano il lavoro degli sviluppatori che vogliono passare da

un’architettura standard alla loro.

Le considerazioni relative alla licenza possono influenzare

la scelta del tipo di core e di FPGA quando l’obiettivo è im-

plementare un progetto sotto forma di circuiti ASIC a celle

standard. Alcune MCU di tipo soft sono concesse in licenza

solo se utilizzate con i dispositivi di un determinato fornito-

re di FPGA. Questo limita la possibilità di un progettista di

trasferire un progetto in un’implementazione di tipo ASIC. Il

vantaggio di questi core di MCU è il completo supporto del

flusso di progetto e di implementazione, con conseguente

semplificazione delle fasi di integrazione di blocchi IP e di

sviluppo successivo.

Per il microprocessore “soft” LatticeMico32 l’accordo di licen-

za è invece caratterizzato da una maggiore flessibilità: Lattice

consente di utilizzare questo core in progetti che prevedono

la migrazione verso circuiti ASIC forniti da fonderie indipen-

denti o anche verso altre architetture FPGA.

Fig. 2 – Schema a blocchi di un HPS (Hard processor System) dei SoC Fpga

di Altera che prevede due core ARM Cortex A-9