DIGITAL

RADAR EMBEDDED

ne è disponibile per i principali

fornitori ed è compatibile con le

disposizioni di riduzione delle

sostanze pericolose contenute

nella Direttiva europea RoHS.

Radar open loop

Il microcontrollore MPC577xK e

il radar transceiver chipset pac-

chettizzato MR2001 77 GHz sono

stati progettati per supportare

un sistema radar open loop. In

sistemi di questo tipo, non è ne-

cessaria la presenza di un anel-

lo ad aggancio di fase (PLL) per

generare segnali di chirp lineari

(modulazione FMCW), il che contribuisce ad abbattere i con-

sumi energetici. Generalmente il concetto di open loop viene

utilizzato congiuntamente a una modulazione FMCW rapida

dei segnali di chirp in un tempo compreso tra 10 e 100

μ

s.

Sistemi veloci di modulazione dei segnali di chirp abbrevia-

no il ciclo di lavoro e migliorano il rapporto segnale-rumore

(SNR) di un sistema radar poiché un’immagine radar completa

viene intercettata più rapidamente. Lo svantaggio potenziale

legato a elevate frequenze in banda base sta nel fatto che si-

ano necessari una maggiore larghezza di banda analogica e

maggiori frequenze di campionamento dell’ADC. Il microcon-

trollore MPC577xK risolve questo problema potenziale perché

integra fino a 8

ΣΛ

-ADC con una larghezza di banda di 5 Mhz

e un clock di campionamento interno da 320 Mhz. In un siste-

ma radar open loop il microcontrollore è il chirp master e un

convertitore analogico-digitale fornisce la tensione di sintonia

al VCO. Sulla base di questo valore di tensione, il VCO genera

un segnale ad alta frequenza (LO) che a sua volta comanda

trasmettitori e ricevitori. Durante il normale funzionamento,

vengono trasmessi segnali di chirp lineari e ricevuti segnali

riflessi. I ricevitori e il trasmettitore sono disposti in un siste-

ma omodina, per cui i segnali ricevuti vengono convertiti di-

rettamente nella banda base. Successivamente questi segnali

di banda base sono filtrati e amplificati (nei chip di ricezione

sono implementati filtri e amplificatori a guadagno variabile)

e inviati in modo differenziato al

ΣΛ

-ADC del microcontrollo-

re MPC577xK. La conversione in forma digitale dei segnali di

banda base, l’applicazione del metodo della formazione del fa-

scio digitale e l’uso di FTT e di algoritmi di tracking permettono

di rilevare oggetti in base a distanza, velocità e angolazione.

Le applicazioni radar

Il microcontrollore MPC577xK è adatto alle applicazioni radar

che potrebbero richiedere fino a un massimo di 8 antenne cia-

scuna, con l’acquisizione simultanea di un massimo di 2048

possibili campioni che vengono successivamente convertiti

da un

ΣΛ

-ADC 12 bit a una velocità di campionamento che

può raggiungere i 10 milioni di campioni al secondo per se-

gnale di chirp.

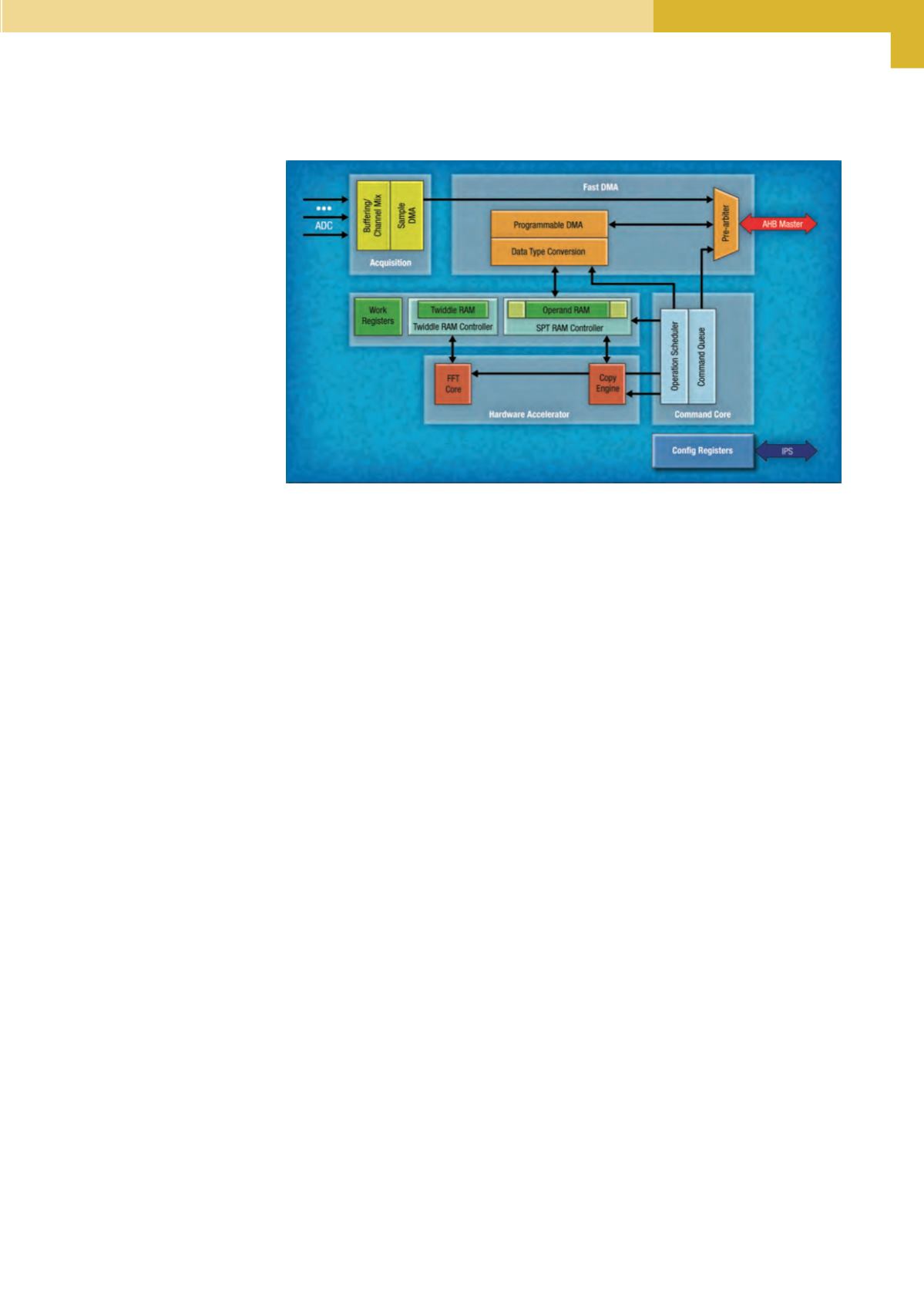

Questo risultato può essere ottenuto tramite la nuova architet-

tura ADC a 8 canali di Freescale unitamente al filtro decimato-

re flessibile/programmabile e a filtraggio anti alias incorpora-

to. Il prodotto è stato anche progettato con un ottimo grado di

immunità al rumore di substrato ed è completamente isolato

dalle altre periferiche del microcontrollore pur conformandosi

agli obiettivi di un consumo energetico ridotto per le applica-

zioni a basso consumo.

Dopo aver acquisito un ciclo di misurazione che potrebbe

consistere di 256 segnali di chirp, questi dati vengono pre-

elaborati utilizzando un blocco di acquisizione dati on-chip e

raggruppati in base alle antenne. Successivamente i campioni

vengono trasmessi alla SRAM del sistema utilizzando l’acces-

so diretto alla memoria (DMA). Il modulo di acquisizione dati

riceve i campioni dal SDADC e li estrae nella finestra di acqui-

sizione.

Dopo l’acquisizione di tutti i dati relativi a un segnale di chirp, i

dati vengono trasferiti alla SRAM locale dello SPT tramite il mo-

tore DMA programmabile e trasformati in base alla frequenza

attraverso il nuovo motore FTT embedded. Il modulo FTT acce-

lerato a livello hardware è in grado di eseguire FTT comples-

se e reali di lunghezza configurabile nonché un’operazione di

windowing che può essere calcolata con i dati.

Il modulo FTT è in grado di eseguire FTT a numeri interi 16-24

bit fino a 4000 punti e dati reali 2x per complesso. A fini di ulte-

riore elaborazione, i dati possono essere trasferiti nella SRAM

del sistema o direttamente alle memorie locali TCM (tightly

coupled memories) della CPU, dove possono essere elaborati

dai core e200z7 che utilizzano SPE2 (una unità di esecuzione

Fig. 4 - Applicazioni radar

47

- ELETTRONICA OGGI 448 - SETTEMBRE 2015