ANALOG/MIXED SIGNAL

TIMING

36

- ELETTRONICA OGGI 444 - APRILE 2015

Lvpecl o CML mentre in uscita si può scegliere fra 2, 4, 6, 8 o

12 linee differenziali esclusivamente di tipo Lvds. Tutti i mo-

delli 8P34S11xxI sono configurati per una tensione di lavoro

di 1,8 V e una frequenza di clock che si può selezionare da 0

fino a ben 1,2 GHz mentre il package è Vfqfn con 16 pin nei

primi due e poi 20, 28 e 40 a salire, tutti con tolleranza termi-

ca fra -40 e +85 °C. La precisione offre uno skew di 20 ps e

un jitter di 42 fsrms sul modello base con due uscite mentre

negli altri modelli skew e jitter diventano rispettivamente di

14 ps e 42 fsrms, 20 ps e 39 fsrms, 20 ps e 41 fsrms e, infine,

12 ps e 73 fsrms nel modello con dodici uscite.

Anche per connessioni PCIe

Micrelha introdotto tre nuovi buffer per la distribuzione del

clock. SY73551L accetta un ingresso di tipo Lvcmos oppu-

re Lvttl e fornisce quattro uscite dello stesso tipo alla stessa

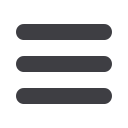

Fig. 4 – Sono quattro le ver-

sioni dei buffer Microsemi

con due ingressi multifor-

mato e otto uscite Lvds

oppure Lvpecl che conten-

gono il jitter fino a 34 fsrms

a 750 MHz

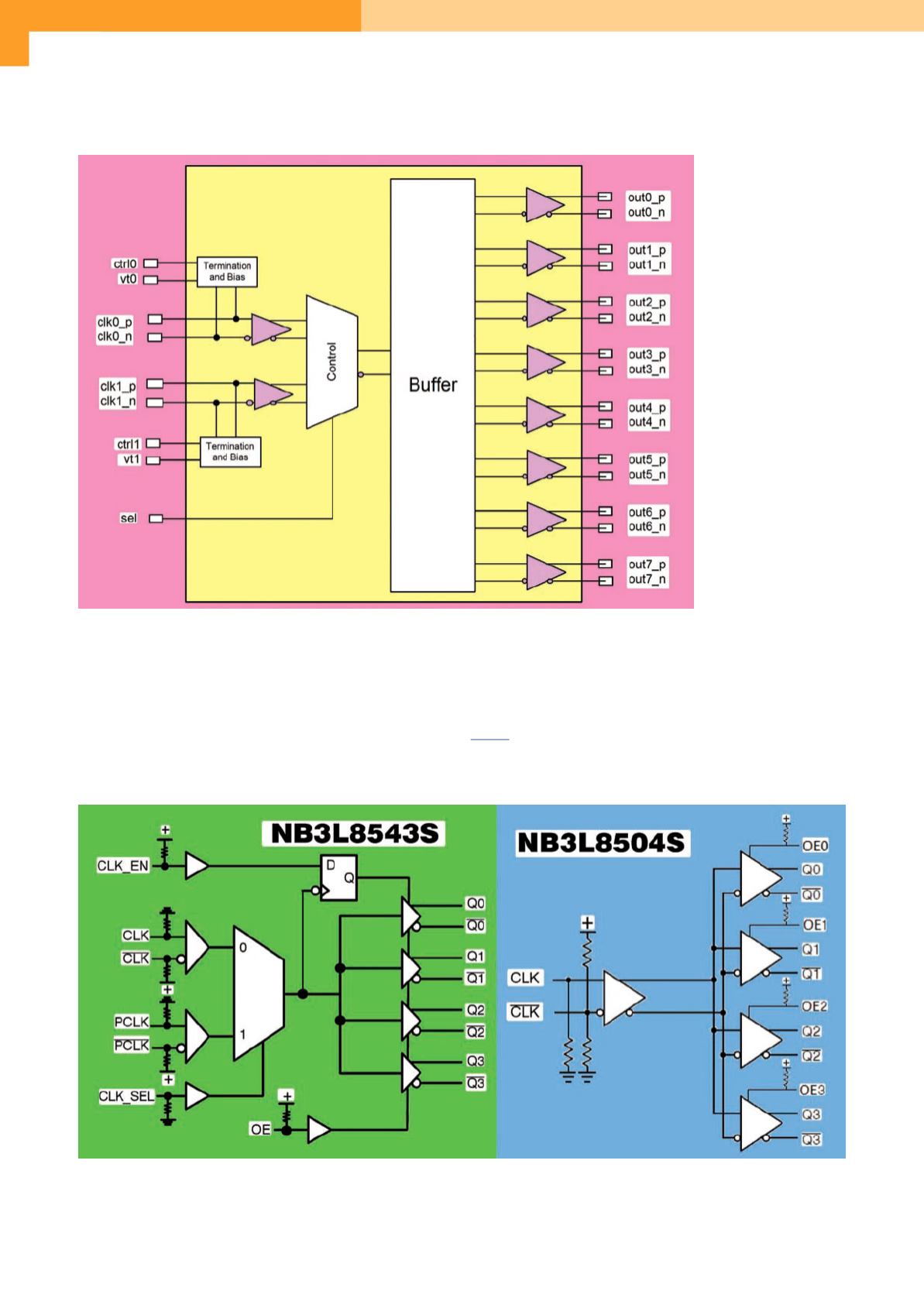

Fig. 5 – Hanno quattro uscite differenziali LVDS con tensione da 2,5 a 3,3V i due nuovi buffer che ON Semiconductor propone con o senza ingresso

multiplexato