ANALOG/MIXED SIGNAL

TIMING

35

- ELETTRONICA OGGI 444 - APRILE 2015

Buffer multiformato

Oggi i buffer per distribuire il clock sono forniti prevalen-

temente con ingresso singolo o differenziale di tipo Lvttl

(Low Voltage Transistor-Transistor Logic) o Lvcmos (Low

Voltage Complementary Metal Oxide Semiconductor) adatto

anche per i tipici oscillatori al cristallo e da due fino a una

dozzina di uscite multiple simili oppure di tipo Lvpecl (Low

Voltage Positive Referenced Emitter Coupler Logic), Lvds

(Low Voltage Differential Signaling), Hcsl (High Speed Cur-

rent Steering Logic), Hstl (High Speed Transceiver Logic)

e/o CML (Current Mode Logic). Fra le caratteristiche tipi-

camente indicate nelle note tecniche di questi dispositivi ci

sono le tensioni dei clock generalmente proposte nei valori

più comuni di 1,8 V, 2,5 V e 3,3 V, nonché le loro frequen-

ze che possono variare da un centinaio di MHz fino a oltre

un GHz in funzione dell’applicazione dove sono installati.

Inoltre, ci sono anche due errori medi tipici che possono

essere causati dall’accoppiamento fra i clock multipli vicini

o dalla loro reciproca interferenza elettromagnetica e sono

lo “skew” che misura la massima differenza temporale che

può intercorrere fra i clock multipli generati in uscita e il

“jitter” che misura l’errore temporale medio che può essere

introdotto dal buffer fra l’uscita e l’ingresso.

A divisione di frequenza

Analog Devicesha realizzato un buffer divisore che consente

di generare i clock in uscita con frequenza inferiore a quel-

la del clock d’ingresso. Il buffer AD9508 accetta all’ingres-

so clock differenziali fino a 1,65 GHz oppure single-ended

fino a 250 MHz e produce quattro uscite differenziali di tipo

Lvds e Hstl con frequenza massima di 1,65 GHz che possono

essere configurate anche come otto single-ended Cmos da

250 MHz. Grazie al preciso regolatore interno a basso dro-

pout la frequenza può essere divisa per 1, 2, 4, 8 o 16 e otte-

nere in uscita clock differenziali di 1650, 825, 412,5, 206,25 o

103,12 MHz. La tensione di lavoro va da 2,375 a 3,465 V con

skew inferiore a 48 ps e jitter di 115 fsrms su tutta la banda

che però scendono a 41 fsrms alle frequenze più basse. Il

package è Lfcsp da 24 pin con tolleranza termica da -40 a

+85 °C ma c’è anche una più recente versione AD9508-EP

per applicazioni militari e aerospaziali con tolleranza termi-

ca estesa da -55 a +105 °C.

Dodici uscite differenziali

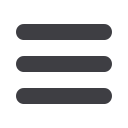

IDTha rilasciato cinque nuovi veloci buffer a basso consu-

mo con ingresso differenziale che può essere di tipo Lvds,

Fig. 2 – Si possono scegliere con 2, 4, 6, 8 o 12 uscite Lvds i buffer IDT

8P34S11xxI che consentono di selezionare la frequenza del clock da 0

fino a ben 1,2 GHz

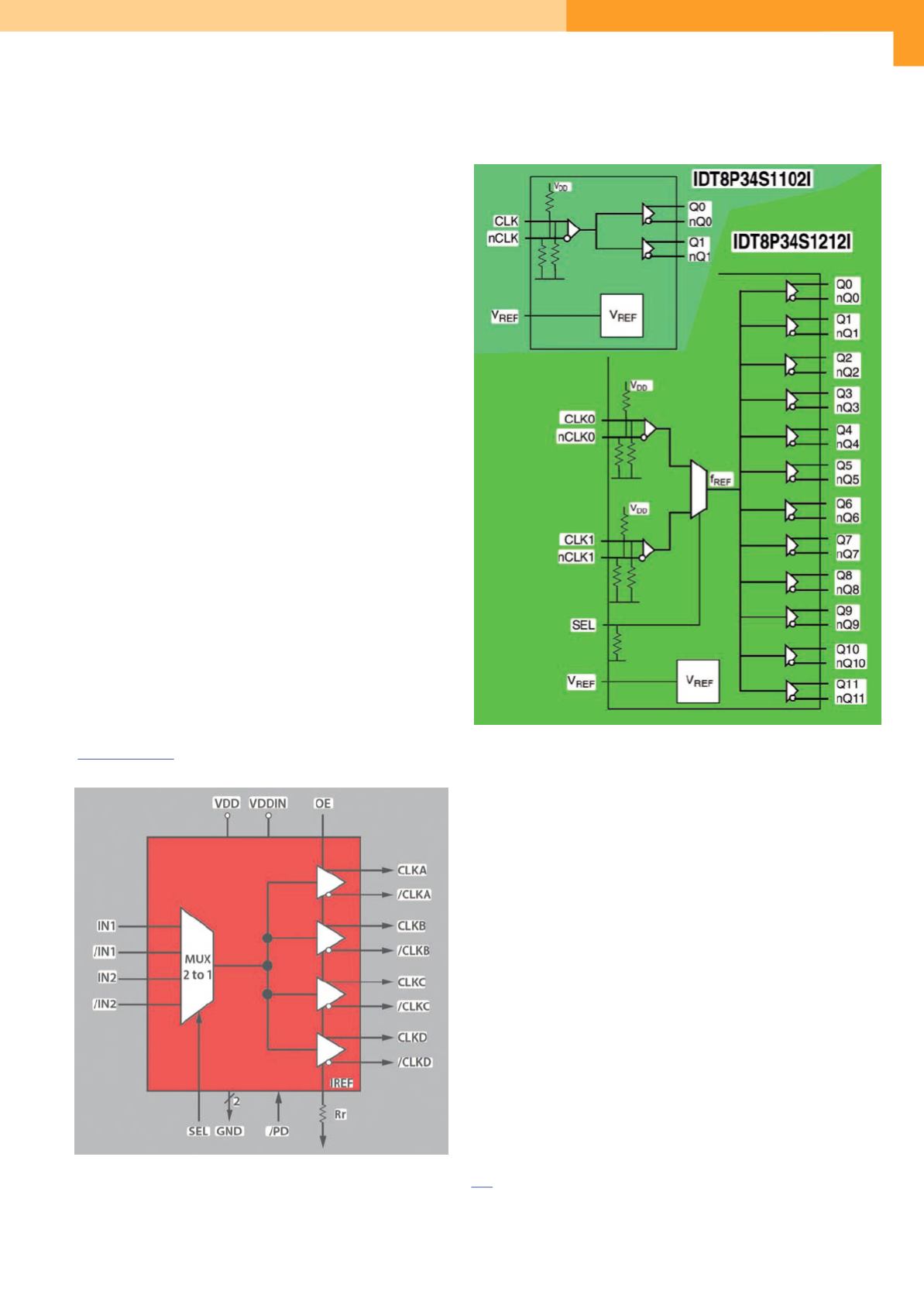

Fig. 3 – Schema funzionale del buffer Micrel SY75576L con due ingressi

multiplexati e quattro uscite Lvds o Hcsl adatte alle connessioni PCIe

con clock fino a 267 MHz