ANALOG/MIXED SIGNAL

TIMING

34

- ELETTRONICA OGGI 444 - APRILE 2015

Integrati per la

temporizzazione distribuita

L

a grande quantità di sottosistemi presenti

nelle moderne schede elettroniche richiede

una rete di distribuzione del segnale di tem-

porizzazione capace di sincronizzare selettivamente

i dispositivi presenti in modo da garantire la corretta

sequenzialità funzionale di tutte le parti del sistema.

Questa rete, innanzi tutto, deve tenere conto che

per i sottosistemi più lontani dall’oscillatore di clock

occorre compensare il maggior tempo di propa-

gazione rispetto ai sottosistemi più vicini in modo

che siano effettivamente sincroni e, inoltre, deve

offrire dei percorsi dedicati per i sottosistemi che

necessitano invece di essere asincroni rispetto agli

altri. Fondamentale è la presenza di quegli integrati

capaci di ricevere all’ingresso un segnale di clock e

offrirne in uscita svariate repliche sincrone che ven-

gono poi trasferite ai vari sottosistemi con opportuni

buffer di ritardo interposti nei tragitti più lunghi. La

capacità di un integrato di pilotare più uscite viene

detta anche fan-out e più alto è il suo valore e più

repliche sincrone del clock all’ingresso si possono

generare. In teoria se tutti i chip avessero l’impe-

denza d’uscita nulla e quella d’ingresso infinita si

potrebbero distribuire infiniti clock ma in pratica

lo stadio d’uscita di ogni chip ha un’impedenza finita che

limita in uscita la massima corrente erogabile alla tensione

prefissata per i simboli binari e perciò stabilisce il massi-

mo numero di chip che si possono collegare continuando

a distinguere senza errori il valore dei simboli trasferiti.

Inoltre, l’impedenza d’ingresso dei chip presenta sempre

una componente capacitiva che rallenta questi collegamenti

e perciò soprattutto nei sistemi con clock particolarmente

elevato va tenuto conto di questi ritardi che dipendono dallo

stadio d’ingresso dei chip ai quali il clock deve arrivare o

meglio dalla loro impedenza in funzione della frequenza

oltre che dalla distanza percorsa.

A complicare le reti di distribuzione del clock si sono oggi

diffuse le implementazioni dove occorre far convivere più

segnali di clock diversi e incompatibili perché relativi a do-

mini funzionali differenti come nel caso delle schede che

montano insieme sottosistemi analogici e digitali. In questi

casi non è detto che occorrano più generatori di clock per-

ché ci sono integrati che consentono di dividere la frequenza

base ottenendo clock multipli da un solo oscillatore. Inoltre,

ci sono anche sistemi con sottoreti suddivise in domini dov’è

possibile imporre periodi limitati nei quali il clock viene dimi-

nuito dai buffer o addirittura fermato quando i sottosistemi

presenti nella sottorete non sono utilizzati e perciò si può

evitare che consumino energia inutilmente. Queste varianti

complicano molto il layout delle schede ma possono essere

vantaggiose soprattutto nelle schede che ospitano numerosi

sottosistemi con funzioni specifiche.

Lucio Pellizzari

Per realizzare sistemi multifunzionali efficienti

sono indispensabili i chip che consentono di

distribuire i segnali di temporizzazione a tutti

i sottosistemi ospitati nelle schede

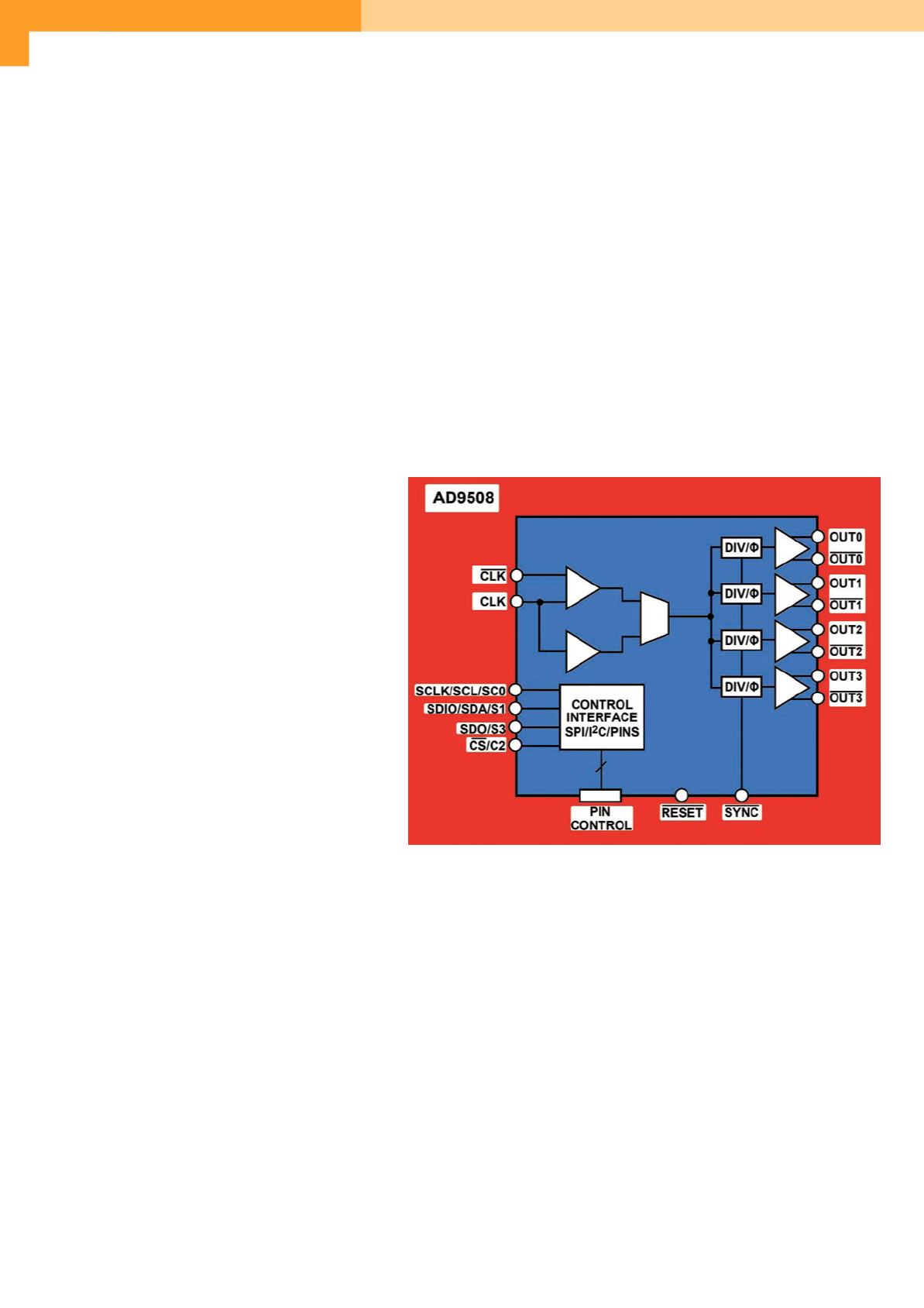

Fig. 1 – Il buffer Analog Devices AD9508 ha quattro uscite configurabili come single-

ended Cmos oppure differenziali Lvds e Hstl con frequenza di 1,65 GHz che può

essere divisa per 1, 2, 4, 8 o 16