EMBEDDED

61 • SETTEMBRE • 2016

38

IN TEMPO REALE

|

NAND 3D

vato dal fatto che le nuove tecnologie NAND

tendono a richiedere la presenza, all’interno

dei controller, di engine per gli algoritmi di

' ##

Error Correction

Code

) sempre più potenti. Un altro problema

importante è che a fronte di una riduzione del-

À

bit per cella, diminuisce la durata delle celle.

Lo sviluppo dei controller NAND host è quin-

di diventato un elemento essenziale nell’am-

biente delle memorie e, in generale, spesso oc-

corre attendere l’adeguamento dei controller

al ridimensionamento del

die

.

Superare i limiti della litografia

Per risolvere il problema legato alla riduzione del-

le dimensioni del

die

e all’aumento della densità di

bit, i produttori di semiconduttori hanno sviluppa-

to alcune modalità per impilare più celle e realiz-

zare così strutture NAND tridimensionali.

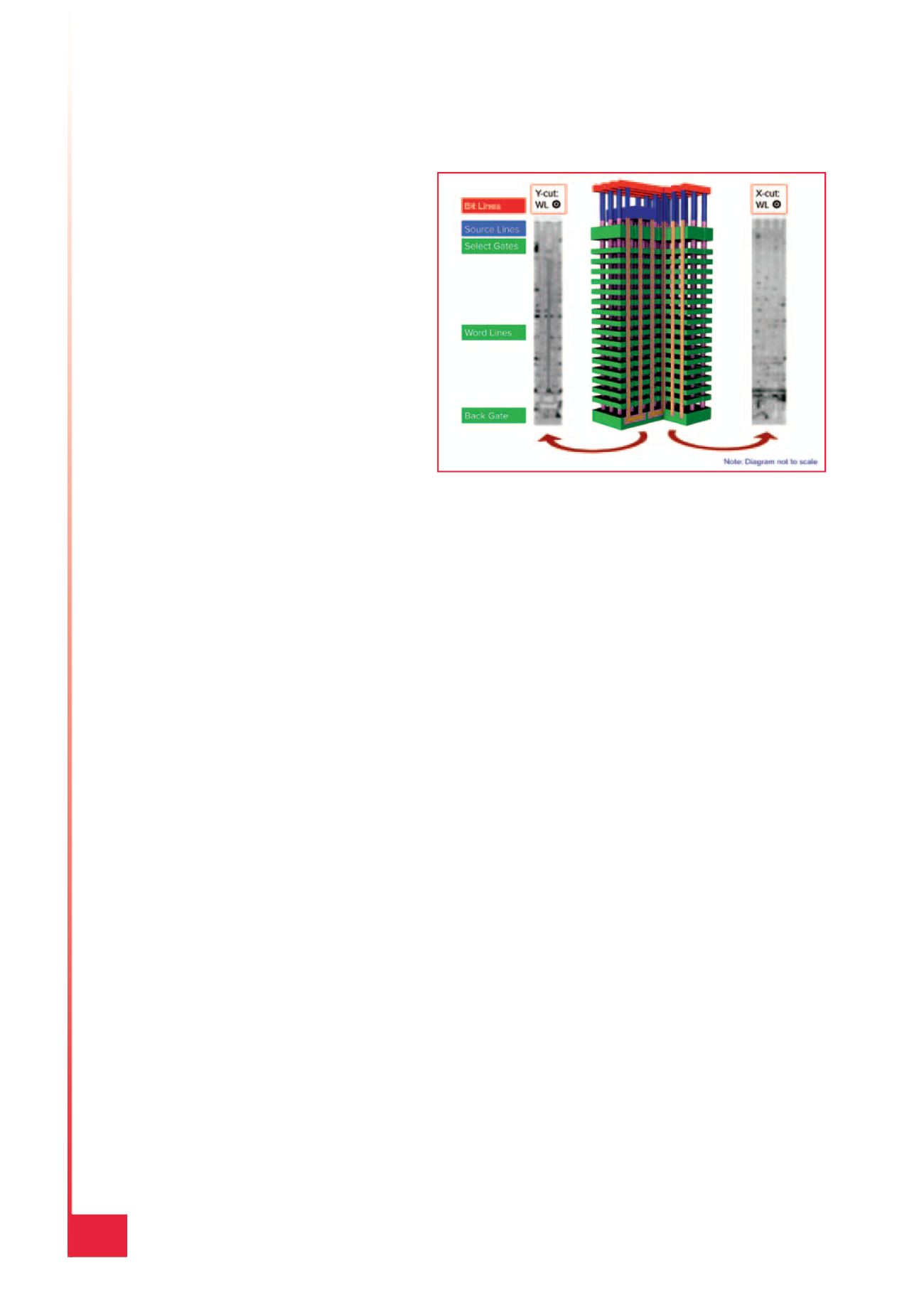

L’idea fondamentale della NAND 3D è quella di

Á

su un substrato di silicio, in modo da aumentare

considerevolmente la densità di bit rispetto alle

Á B,B=

À

Á

struttura a celle tridimensionali a 48 livelli de-

7 # '

Bit Column Stacked

) che supera

di gran lunga la capacità delle classiche memorie

Á B,B=

-

% À -

|

cancellazione e rendendo la scrittura più veloce.

&%

% À -

|

-

lazione è dovuta al fatto che la nuova tecnologia

7 #

À $

À

densità di bit. Di fatto, la durata e l’aumento di af-

À -

|

H

-

vate che, non solo i dispositivi a celle multilivello

'5&#E C

(

' &#E

per cella) sono ormai prossimi alla produzione di

massa, ma si stanno anche prendendo in conside-

razione dispositivi con 4 bit per cella.

Nel prossimo futuro, Toshiba prevede la coesisten-

B,B= C= <=

7 #

essendoci sovrapposizione nelle capacità offerte

5 B,B= C=

- 4C:

7 #

possono senz’altro superare questo limite. Toshiba

Á 7 #

=

per sistemi di cloud storage di grandi dimensioni.

À

dispositivi è l’impiego da parte delle architetture

7 #

'

charge trap

), che

memorizzano elettroni in uno strato costituito da

nitruro di silicio anziché da silicio policristallino

drogato, anziché della tipica struttura con celle a

Á

'

) utilizzata storicamen-

B,B= C= '! 4( )

celle di memoria a trappola di carica sono di gran

lunga più longeve rispetto alle tradizionali celle a

Á

&

Á

-

te a un bicchiere pieno d’acqua, in cui anche una

E ?

a riconsiderarne il valore in termini di resistenza

e longevità. In confronto, gli strati di memoria con

celle a trappola di carica sono simili a spugne, in

grado di memorizzare una certa quantità di acqua

anche se parte della spugna si rompe, con chiari

vantaggi in termini di resistenza e di durata.

&

7 #

-

% À

9

consente la fabbricazione in stabilimenti già ope-

'

À (

-

7 #

À

5

À %

-

' 8&

Extreme UltraViolet

Lithography

(

À

'B &

Nanoimprint Lithography

) permetterà di realiz-

zare disegni ben più complicati, con conseguenze

favorevoli sulla versatilità della progettazione.

Poiché la spaziatura tra le celle è maggiore, il ru-

Fig. 1 – NAND BiCS con celle a trappola di carica

(

charge trap

)