Rilasciato il test chip del processore EPAC1.0 RISC-V di EPI

L‘European Processor Initiative (EPI), un progetto con 28 partner di 10 Paesi europei con l’obiettivo di aiutare l’UE a raggiungere l’indipendenza nelle tecnologie dei chip HPC e nell’infrastruttura HPC, ha annunciato il rilascio del test chip EPAC1.0 per la fabbricazione.

Un segmento chiave delle attività EPI è lo sviluppo e la dimostrazione di IP di processori interamente sviluppati in Europa basati sull’architettura del set di istruzioni RISC-V, fornendo i core per acceleratori efficienti dal punto di vista energetico e ad alto rendimento denominati EPAC (European Processor Accelerators).

L’utilizzo dell’architettura del set di istruzioni RISC-V consentirà di sfruttare le risorse open source a livello di architettura hardware e software, oltre a garantire l’indipendenza dalle tecnologie informatiche brevettate non europee.

EPAC combina diverse tecnologie di accelerazione specializzate per diverse aree applicative.

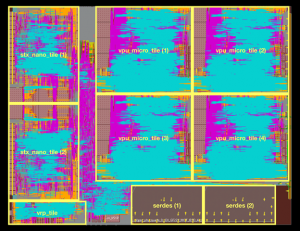

Il chip di test contiene quattro micro-tiles di elaborazione vettoriale (VPU) composte da un core Avispado RISC-V progettato da SemiDynamics e un’unità di elaborazione vettoriale progettata dal Barcelona Supercomputing Center e dall’Università di Zagabria.

Ogni tile contiene anche un Home Node e una cache L2, progettati rispettivamente da Chalmers e FORTH, che forniscono una visione coerente del sottosistema di memoria. L’acceleratore Stencil e Tensor (STX) è stato progettato da Fraunhofer IIS, ITWM e ETH Zürich e il processore a precisione variabile (VRP) da CEA LIST. Questi acceleratori specializzati sono collegati su chip con una rete ad altissima velocità e tecnologia SERDES di EXTOLL.

Il progetto EPAC è stato finalizzato da Fraunhofer IIS per l’integrazione del chip con tecnologia GLOBALFOUNDRIES 22FDX low power e sarà integrato e valutato nella scheda basata su FPGA progettata da FORTH, E4 e dall’Università di Zagabria.

Contenuti correlati

-

Un processore con LPDDR4 integrata accelera lo sviluppo di applicazioni

Il System-in-Package rappresenta una valida scelta di progettazione e può essere determinante per lo sviluppo di svariate applicazioni e dispositivi di tipo general purpose, nonché per soluzioni compatte e ad alte prestazioni Leggi l’articolo completo su EO519

-

CEVA presenta l’architettura di processore NeuPro-M

CEVA ha annunciato NeuPro-M, la sua architettura di processore di ultima generazione per applicazioni di intelligenza artificiale e machine learning. Destinata ai mercati di Edge AI e Edge Compute, NeuPro-M è un’architettura eterogenea autonoma composta da più...

-

Il processore Arm in plastica

Su Nature recentemente è stato pubblicato uno studio relativo a un processore Arm flessibile a 32 bit. Il nome è PlasticARM ed è stato implementato utilizzando un processo produttivo di Pragmatic a 0,8 μm e tool di...

-

Il processore per applicazioni spaziali di Teledyne e2v supera i test TID

Teledyne e2v ha annunciato che il suo processore LS1046-Space ha superato i severi test TID (total ionizing dose) per le radiazioni, raggiungendo una resilienza di 100krad. Questi risultati completano quelli precedentemente ottenuti in termini di singolo evento...

-

Dai tablet ai server fino al cloud: il nuovo Ceo di Intel snocciola novità all’IDF

Brian Krzanich, nuovo amministratore delegato di Intel, ha fatto il suo debutto all’Intel Developer Forum (IDF) che si è tenuto nella prima decade di settembre e si è imposto sottolineando come Intel voglia affrontare ogni segmento del...

-

DisplaySearch: il dominio Arm nei tablet durerà fino al 2013

In base ai dati di uno studio condotto da DisplaySearch, per la fine dell’anno verranno spediti 59,9 milioni di tablet basati su Arm. Un elemento che potrebbe giocare a favore delle piattaforme x86...

-

Adlink: MXE-5000 il nuovo PC fanless con Intel Core 2 DUO

MXE-5000 di Adlink (Goma Elettronica) è ideale per applicazioni di sorveglianza, controllo, automazione e impiego navale (certificato IEC-60945) che richiedano una piattaforma affidabile e versatile, capace di operare in...

-

Kontron: scheda processore CP6003-SA in formato CompactPci 6U

La scheda processore CP6003-SA, disponibile in formato CompactPci 6U e basata sui processori mobili Intel Core i5/i7 di seconda generazione, è stata progettata da Kontron per garantire elevate prestazioni a fronte di consumi decisamente contenuti...

-

L’RTOS Micrium supporta la piattaforma di sviluppo PsoC 5 di Cypress basata su ARM Cortex-M3

Cypress Semiconductor e Micrium hanno annunciato che il sistema operativo in real time (RTOS) uC/OS-III di quest’ultima supporta la piattaforma di sviluppo PSoC di Cypress Semiconductor.

-

Arm Cortex.M0 disponibile anche via DesignStart online IP portal

Alla presenza di 200 visitatori, principalmente provenienti dalla General Industry, l’azienda all’avanguardia nel settore della robotica ha presentato le sue ultime novità direttamente in fabbrica, dove i robot sono progettati, costruiti e collaudati per poi essere spediti in...