L’EDA entra nell’era della verifica 3.0

Nell’analisi della correttezza dei chip, gli strumenti di electronic design automation approdano alla fase evolutiva della verifica system-level. La visione di Mentor Graphics alla base del lancio della nuova piattaforma EVP

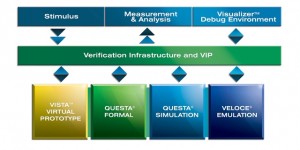

È stata annunciata lo scorso aprile da Mentor Graphics e la sua disponibilità generale con tutti i relativi componenti è prevista a partire da giugno: l’introduzione della Enterprise Verification Platform (EVP) segna, secondo l’azienda, una svolta tecnologica epocale. Vuole infatti rappresentare l’ingresso nell’era del ‘sistema’ e della verifica 3.0, che giunge dopo aver attraversato per lunghi anni le fasi storiche della verifica 1.0, imperniata su linguaggi come RTL e VHDL, e della verifica 2.0, che poneva l’accento sulle metodologie, la ‘testbench automation’ e il linguaggio SystemVerilog.

Oggi, la grande diffusione e il successo dei SoC (system-on-chip) in moltissimi dispositivi – non solo smartphone e tablet, ma anche console videogiochi, attrezzature di networking, auto, aeroplani, satelliti e quant’altro – sta davvero trasformando profondamente lo scenario tecnologico. È la complessità di progettazione dei SoC che sta conducendo a questa trasformazione. Ma dire complessità non sembra sufficiente, secondo Mentor.

La parola chiave è ‘sistema’ perché, spiega l’azienda, la verifica dei chip oggi è diventata una verifica e una validazione di tipo ‘system-level’. Da ciò consegue che per ingegneri e sviluppatori oggi diventa necessario poter verificare e validare tutti i componenti software assieme a quelli hardware; ma anche poter eseguire molti più cicli di verifica, per ottenere un processo di analisi ‘pre-silicon’ attraverso prove e test guidati dal software. In aggiunta, l’esigenza è sempre più di verificare le interazioni system-level con numerosi core di tipo eterogeneo che accedono a risorse condivise. Infine, sottolinea Mentor, vi è la necessità di unificare la verifica pre-silicon e la validazione post-silicon: un ambito in cui la tecnologia di emulazione gioca un ruolo chiave, perché il modello seguito nelle economia di scala per la verifica dei SoC sta conducendo a introdurre un livello di automazione sempre più spinto in tali processi di analisi.

Il datacenter che ospita i sistemi di emulazione Veloce2, nella sede di Mentor Graphics, a Freemont, California

Emulazione, settore più in crescita nel mondo EDA

Mentor arricchisce la propria offerta con la piattaforma EVP, in un momento in cui, sottolinea, l’uso delle tecnologie di emulazione per la verifica system-level sta diventando un must. È questo il settore che nel mercato EDA sta crescendo maggiormente: il fatturato derivante dalle tecnologie di emulazione mostra una crescita, dal 2010 al 2014, che procede con un CAGR (tasso di crescita annuale composto) superiore al 30%. Gli utenti del settore hanno sempre più l’esigenza di utilizzare soluzioni enterprise-level, capaci di fornire agli ingegneri un ambiente comune, in grado di includere comuni funzionalità di debug, verifica dell’IP, interfacce utente, testbench, asserzioni e quant’altro. Un ambiente unificato per la simulazione e l’emulazione. La novità introdotta con la piattaforma EVP è poi che macchine di emulazione come quelle della famiglia Veloce2 si possono ora far migrare, dal laboratorio, agli ambienti di data center, diventando completamente gestibili in modalità remota, come dei normali server.

Risorsa ospitata nel data center

Un componente chiave in EVP è Veloce OS3, un nuovo sistema operativo per l’emulazione. In effetti, l’Enterprise Server OS3 è in grado di gestire le risorse globali di emulazione in maniera efficiente, consolidandole virtualmente in una singola entità, condivisibile a livello enterprise e dotata di elevata capacità computazionale. Come dichiara Mentor, l’Enterprise Server può determinare la location remota più efficiente e adatta a eseguire ciascuna analisi di verifica, ed elaborare immediatamente i job ad alta priorità, sospendendo temporaneamente quelli a priorità più bassa.

Le sue funzionalità consentono di eliminare cavi, adattatori, dispositivi fisici delle attrezzature ICE (in-circuit emulation), sostituendoli con dispositivi virtuali. Le periferiche di VirtuaLAB Veloce OS3 sono inoltre subito riconfigurabili, per supportare diversi progetti o nuove priorità, e ciò è possibile grazie al fatto che VirtuaLAB è ospitato nel data center su computer standard, e non su hardware proprietario. Veloce OS3 fornisce all’emulatore anche evolute funzionalità di verifica, che includono le asserzioni PSL e SystemVerilog, la copertura funzionale, e il supporto UPF (unified power format) per la verifica dei sistemi low-power. In questo modo, dice Mentor, è possibile fornire alte prestazioni nelle attività di verifica e analisi pre-silicon di sottosistemi SoC critici su cui gira software applicativo.

La complessità dei SoC fa spendere ai team di progetto una larga parte del tempo di verifica nelle attività di debug, e per migliorare la produttività in quest’area il nuovo ambiente Visualizer si pone come una singola soluzione di debug, strettamente integrata nelle funzionalità di simulazione ed emulazione. Visualizer permette di eseguire varie operazioni di debug (debug RTL, gate-level e testbench; tracciamento automatico per l’individuazione rapida degli errori; debug a livello di protocollo e transaction-level). Possiede anche un insieme completo di funzionalità di debug native UVM e SystemVerilog, e supporta il debug UPF low-power. Tutte queste funzionalità sono disponibili sia in modalità interattiva, sia in post-simulazione, per la simulazione e l’emulazione.

Il software rappresenta un’enorme componente nella verifica dei SoC: per velocizzarne il signoff, la EVP, attraverso il tool Codelink, unifica il debug del software, supportando i motori di verifica Questa e Veloce OS3, e facendo leva sull’emulazione.

Un altro problema riguarda il fatto che, in molti progetti SoC, i dati di verifica provengono da molteplici fonti, che devono poter essere fuse e analizzate in maniera olistica, per accertare l’effettiva completezza del sistema. Qui, attraverso Veloce OS3 e Questa 10.3, le asserzioni e le varie fonti di dati (coverage, runtime, emulazione, simulazione mixed-signal, low-power e così via) sono scritti in un database ad alte prestazioni. In questo modo, utilizzando un database comune e gli strumenti Questa Verification Management, i team di verifica, collettivamente, sono in grado di migliorare ulteriormente i tempi di debug.

Giorgio Fusari

Contenuti correlati

-

Partnership tra Altair e Samsung Electronics

Altair ha annunciato di essere stata scelta come partner per l’automazione della progettazione elettronica (EDA) per il Samsung Advanced Foundry Ecosystem (SAFE). Questa collaborazione permetterà di combinare la tecnologia EDA di Altair, compresi gli strumenti per il...

-

Certificazione ISO 26262 per l’ambiente di progettazione FPGA di GOWIN

GOWIN Semiconductor ha annunciato che il suo ambiente di progettazione FPGA GOWIN EDA è stato certificato conforme agli standard di sicurezza funzionale ISO 26262 e IEC 61508 dal laboratorio di test TUV. La certificazione del design tool...

-

La nuova soluzione Veloce CS di Siemens per migliorare l’emulazione e la prototipazione

Siemens Digital Industries Software ha presentato Veloce CS, un sistema di verifica e di validazione hardware-assisted che integra all’interno di un unico sistema l’emulazione hardware, la prototipazione di livello enterprise e la prototipazione software. Questa soluzione rappresenta...

-

Synopsys acquisisce Ansys

Synopsys e Ansys hanno annunciato di aver siglato un accordo definitivo in base al quale Synopsys acquisirà Ansys. Le aziende sottolineano che la combinazione della tecnologia EDA di Synopsys con le capacità di simulazione e analisi di...

-

La tecnologia di simulazione di Siemens EDA scelta da RS Group

Siemens Digital Industries Software ha annunciato che RS Group ha scelto Siemens come fornitore strategico di automazione della progettazione elettronica (EDA) per il suo nuovo strumento DesignSpark Circuit Simulator, cloud nativo, che consente agli utenti di ottimizzare...

-

Prospettive di mercato per il 2023: quattro macro-tendenze da monitorare nella progettazione degli IC

Di Joe Sawicki, Executive Vice President of IC EDA – SIEMENS Nonostante le incertezze legate all’attuale contesto economico e geopolitico, il 2022 è stato un anno stellare per l’innovazione in campo elettronico, e sono sicuro che nel...

-

RECOM collabora con SAMACSYS per i modelli EDA

RECOM ha annunciato una partnership con SAMACSYS, una società di Supplyframe, per fornire modelli digitali di prodotti RECOM. Simboli, footprint e modelli CAD 3D sono disponibili gratuitamente in un gran numero di formati, compresi STEP e VRML,...

-

Machine learning: la rivoluzione nella progettazione dei chip

La completa automazione della stesura del layout consentirà di progettare sistemi hardware nel giro di 24 ore. Negli ultimi 20 anni, e anche più, le aziende operanti nel settore EDA (Electronic Design Automation) hanno focalizzato la loro...

-

Accordo fra Boeing e Siemens per il software Mentor Graphics

Siemens ha annunciato di aver stretto un accordo con Boeing per estendere l’uso del software Mentor Graphics all’iniziativa Second Century Enterprise Systems (2CES) per la trasformazione dell’azienda. Questa scelta deriva da un’analisi delle soluzioni disponibili in termini...

-

Misure di sicurezza avanzate per i dispositivi medicali indossabili

Nell’ambito del settore sanitario è di fondamentale importanza che la memorizzazione e la trasmissione delle informazioni personali avvenga in un formato che consenta l’accesso ad esse in tempo reale ma al contempo garantisca robusti livelli di protezione che...