DAQ (parte 3) – Timing system e filtering

Nei sistemi DAQ è necessaria la progettazione di stadi temporali per la sincronizzazione hardware dei vari dispositivi che ne compongono. Contemporaneamente, la gestione e tutela dei dati è un’altra funzione che coinvolgono sistemi di filtraggio.

Un timing system può essere rappresentato da una delle seguenti voci: phase-lock looping, hand-shaking, sincronizzazione su dispositivi RF e così via. Si basano su due presupposti principali: tutti i segnali sono digitali e tutti i componenti condividono un concetto comune e discreto di tempo: viene identificato dal segnale di clock comune al circuito.

I vantaggi di un circuito asincrono possono essere descritti come segue:

- basso consumo energetico;

- elevata velocità di funzionamento;

- migliore modularità;

- robustezza in termini di variazioni di tensione di alimentazione, temperatura e parametri relativi a processi di fabbricazione.

Parametri temporali per logica combinatoria

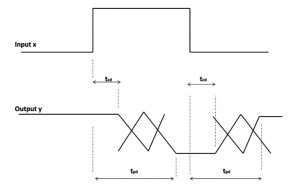

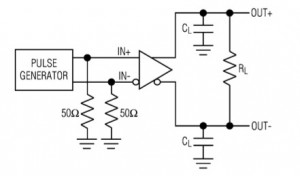

Caratteristiche di temporizzazione possono essere definite dalla figura 1:

• ritardo di propagazione (tpd): intervallo di tempo che intercorre tra l’applicazione di una nuova configurazione agli ingressi di un blocco e la stabilizzazione dei corrispondenti valori dei segnali d’uscita,

• tempo di contaminazione (tcd): intervallo di tempo che intercorre tra l’applicazione di una nuova configurazione agli ingressi di un blocco e la prima variazione riscontrata sui segnali d’uscita.

Parametri temporali per logica sequenziale

I parametri implementati in ambito della logica sequenziale vengono caratterizzati in relazione al segnale di clock.

Latch vs Flip- Flop

Il latch è un circuito bistabile in grado di memorizzare un bit di informazione nei sistemi a logica sequenziale asincrona. Il latch cambia lo stato logico dell’uscita in funzione del segnale d’ingresso (attivo/basso), mentre il flip-flop cambia lo stato logico dell’uscita solamente quando il segnale di clock è nel semiperiodo attivo (positive/negative edge trigger).

Caratteristiche di timing possono essere specificate in relazione al fronte di salita (positive edge-triggered) o di discesa (negative edge trigger) del clock. Alcuni parametri sequenziali possono essere:

• Il ritardo di propagazione (tclk – q): tempo necessario per una variazione del clock di ingresso del flip-flop D, per provocare un cambiamento in uscita Q.

• tempo di contaminazione (tCD): tempo necessario per una variazione del segnale di clock del flip-flop, per implementare una variazione iniziale sull’uscita Q.

• Tempo di Setup (tsu): tempo prima del fronte di salita/discesa del clock dove i dati di input sono mantenuti stabili.

• Tempo di attesa (Thold): tempo successivo al fronte del clock dove l’input di dati del flip flop D devono essere tenuti stabili in modo che il flip- flop possa bloccare il valore corretto.

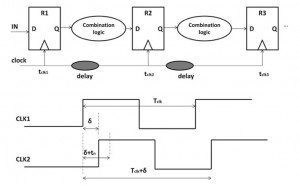

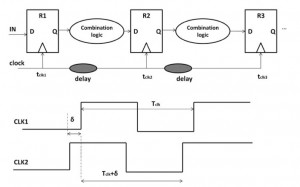

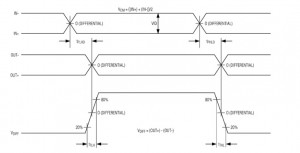

Clock skew è un ritardo del segnale di clock che si genera a causa della topologia della rete di distribuzione dello stesso, sostanzialmente si tratta di una differenza temporale (Figg. 2 e 3). Cause possono essere molteplici: distanza del generatore di clock, fluttuazione della temperatura, imperfezioni dei materiali.

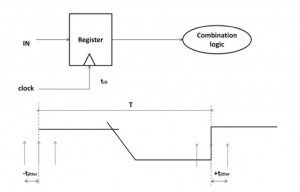

Il clock Jitter, invece, è correlato alla variazione temporale del periodo di clock che può aumentare o diminuire (Fig. 4).

Per jitter, quindi, si intende il fenomeno della irregolarità del clock in un segnale digitale. È facile intuire che poiché in natura non esistono parametri “stabili” qualunque segnale digitale è affetto da jitter (così come qualunque segnale analogico è affetto da rumore).

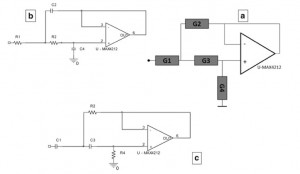

Il MAX9155 (Figg. 5 e 6) è low-voltage differential signaling (LVDS), che accetta un singolo ingresso LVDS e duplica il segnale ad una singola uscita LVDS. Il suo basso jitter lo rende ideale per i segnali buffer LVDS inviati su lunghe distanze o in ambienti rumorosi, come cavi e backplane.

Il package molto piccolo del MAX9155 lo rende particolarmente adatto per ridurre al minimo le lunghezze stub nelle applicazioni backplane multidrop.

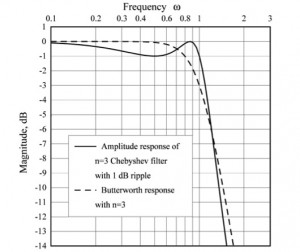

Fig. 7 – Risposta in ampiezza di un filtro di terzo ordine. Filtro Chebishev (linea continua), Butterworth (linea tratteggiata)

Il pacchetto SC70 (metà delle dimensioni di un SOT23) permette al MAX9155 di essere sistemato vicino al connettore, minimizzando così lunghezze stub e riflessioni sul bus. Il collegamento punto a punto tra l’uscita del MAX9155 e la destinazione, come un FPGA o ASIC, permette di trovarsi a distanze maggiori dal connettore bus.

Un filtro è un dispositivo che realizza delle funzioni di trasformazione dati di segnali analogici e/o digitali.

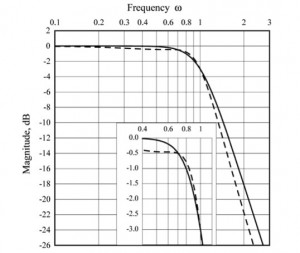

I filtri più comuni sono il Butterworth , Chebyshev, e Bessel (Figg. 7 e 8). Ci sono altri tipi, ma il 90 % di tutte le applicazioni possono essere risolti con uno di questi tre. Il Butterworth garantisce una risposta piatta nella banda passante e un tasso adeguato di roll-off, semplice da capire e adatto per applicazioni quali l’elaborazione audio.

Fig. 8 – Risposta in ampiezza di un filtro Butterworth (linea tratteggiata) e filtro ottimizzato (linea tratteggiata) di terzo ordine

Il Chebyshev fornisce un più ripido roll-off, ma il ripple nella banda passante lo rende inadatto per sistemi audio. È superiore per applicazioni in cui la banda passante comprende una sola frequenza di interesse. Il filtro di Bessel fornisce un ritardo di propagazione costante su tutto lo spettro di frequenza di ingresso. Pertanto, applicando un’onda quadra (costituito da armoniche fondamentali e altre) all’ingresso di un filtro di Bessel si produce un’onda quadra di uscita senza overshoot (tutte le frequenze sono ritardate di pari valore). Altri filtri ritardano le armoniche di quantità diverse con conseguente superamento sulla forma d’onda di uscita.

Nella figura 9 alcuni esempi di passa-basso, passa-alto e il design di un filtro generico. Altri tipi di filtri come quelli digitali, sono algoritmi utilizzati principalmente nei computer. Le principali operazioni che includono sono i seguenti: smoothing (media), integrazione, separazione di segnali (filtraggio) e la stima.

I filtri digitali possono essere confrontati con filtri analogici; ad esempio, il passa basso ha l’equivalente digitale ma hanno in aggiunta alcuni importanti caratteristiche che li rendono adatti solo per il sistema di comunicazione digitale. I filtri digitali, infine, possono essere programmati, quindi dotati di memoria, e non ci sono problemi d’impedenza di corrispondenza.

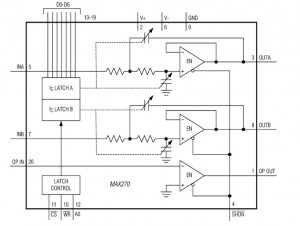

Esempio commerciale è il MAX270/MAX271 (Fig. 10): filtri digitali programmabili passa basso. La loro tipica gamma dinamica di 96 dB lo rendono ideali come anti-aliasing e applicazioni DAC.

Frequenze di taglio nel range 1-25 kHz possono essere selezionate con opportuno codice di programma.

Leggi gli articoli precedenti

DAQ (parte 1) – Sistemi di acquisizione dati: generalità di progettazione

DAQ (parte 2) – Il condizionamento dei segnali e digitalizzazione

Maurizio Di Paolo Emilio

Contenuti correlati

-

Analog Devices: soluzione DAQ μModule di precisione e ad alta velocità

La soluzione per l’acquisizione dati (DAQ) µModule a 16 bit e 15 MSPS di Analog Devices permette la digitalizzazione di segnali transitori veloci nelle applicazioni di power analysis e per l’abilitazione del loop di controllo digitale a...

-

Da Acceed un computer DAQ per applicazioni edge

MCM-204 è un computer disponibile da Acceed per applicazioni di data recording (DAQ) a livello edge. Si tratta di un prodotto estremamente compatto e dotato di quattro ingressi analogici ad alta risoluzione e uscite digitali dedicate che...

-

Murata introduce nuovi convertitori DC-DC da 600 W in formato ¼ brick

Murata Power Solutions ha annunciato nuovi convertitori DC-DC da 600 W in formato ¼ brick basati su un processore ARM a 32 bit. Queste nuove famiglie sono conformi alle specifiche DOSA e supportano i più recenti comandi...

-

DAQ (parte 12) – Software di design PCB e sistemi DAQ commerciali

La progettazione PCB gioca un ruolo fondamentale nei sistemi di acquisizione dati. I software di progettazione diventano, quindi, essenziali per l’ottimizzazione di un sistema elettronico generale. In quest’ultimo articolo ci concentreremo sugli aspetti tecnici e commerciali dei...

-

DAQ (parte 11) – Design di PCB

La progettazione di un PCB è una fase molto importante per realizzare prototipi elettronici efficienti; rappresenta uno degli ultimi step di design ma è quello più critico da cui dipendono le prestazioni operative. Nelle applicazioni di acquisizione...

-

DAQ – Sistemi di acquisizione dati in 12 puntate

La progettazione di sistemi di acquisizione dati (DAQ) consiste in un processo ingegneristico hardware e software in modo da soddisfare le richieste operative. In questa serie organizzata in 12 articoli, analizzeremo le problematiche connesse e progetteremo come...

-

DAQ (parte 10) – Scelta di un trasduttore

La temperatura può avere un grande effetto sull’affidabilità del prodotto, sia esso un sistema di acquisizione dati sia di controllo embedded. Tuttavia, facendo accurate e ripetitive misurazioni di temperatura, non è così semplice come ci si potrebbe...

-

DAQ (parte 9) – Design con FPGA (seconda parte)

Un sistema DAQ-FPGA utilizza un chip FPGA per gestire i dati digitali di un ADC. La FPGA può incorporare il proprio microcontrollore e gestire le funzionalità logiche definite opportunamente dall’utente utilizzando un linguaggio di programmazione speciale chiamato...

-

DAQ (parte 8) – Design con FPGA

In un sistema di acquisizione il flusso di dati può essere gestito da un FPGA che garantisce una notevole trasmissione e una facile riprogrammazione. Analizziamo la FPGA con un esempio di progetto in ambito di un sistema...

-

DAQ (parte 7) – Misura di parametri fisici via USB

Con l’avanzare della tecnologia informatica/elettronica i prezzi calano drasticamente e, quindi, progetti di dispositivi low cost in vari ambiti diventano una necessità. Grandezze fisiche quali temperatura, pressione, umidità, intensità della luce e così via, sono generalmente “lente”...