DAQ (parte 2) – Il condizionamento dei segnali e digitalizzazione

Prosegue la serie, organizzata in 12 articoli, dedicata alla progettazione di sistemi di acquisizione dati (DAQ). In questa serie analizzeremo le problematiche connesse e progetteremo come goal finale un DAQ Embedded. L’obiettivo sarà non solo affrontare le tecniche di progettazione ma avere un certo riguardo anche nel settore commerciale per capire che cosa il mercato ci offre dal punto di vista di sistemi DAQ.

La prima operazione in un sistema DAQ è il condizionamento di segnale. Il segnale proveniente dal sensore deve innanzitutto essere inviato a un sistema elettronico per la conversione in digitale. Tuttavia, per essere utile ai dispositivi di interfaccia, il segnale può essere inviato in alcune forme di condizionamento. In generale, tutti i dispositivi di interfaccia sono progettati per consentire l’interfacciamento dei segnali di rilevamento in un campo di tensione da 0 a 5 V che verrà digitalizzato dal convertitore A / D. In generale, i dispositivi di condizionamento sono progettati per essere flessibili al cambiamento di questo intervallo.

Il processo di condizionamento comporta una combinazione di processi più semplici che possono essere utilizzati in tutti i tipi di segnali: la conversione di una resistenza in una tensione, amplificazione e shifting di una tensione.

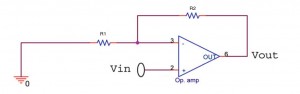

A prescindere dai tipi di sensori o trasduttori, l’equipaggiamento del condizionamento del segnale è in grado di migliorare la qualità e le prestazioni del sistema. Nel circuito di condizionamento del segnale con l’amplificazione (Fig.1), un amplificatore che si trova sulla scheda DAQ o in un dispositivo esterno, applica un guadagno per il piccolo segnale di rilevamento prima di essere inviato in un convertitore analogico- digitale (ADC). Se l’ADC richiede una tensione positiva e sensori producono tensione di uscita – X + X , è necessario spostare la tensione, per esempio, da 0 a 2X Volt.

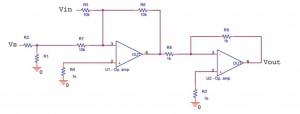

Il circuito per shifting di tensione è più complesso: utilizza una doppia configurazione di amplificatori operazionali per aggiungere una tensione fissa al segnale di ingresso (Fig. 2).

Inoltre, è possibile utilizzare i filtri per eliminare il rumore indesiderato all’interno di un certo range di frequenza. Causa più comune di DAQ danneggiati o problemi su misura è la messa a terra impropria del sistema. Per evitare ciò, è necessario isolare condizionatori di segnale e prevenire la maggior parte di questi problemi.

Esempio di progettazione: un circuito di condizionamento

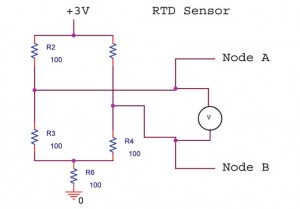

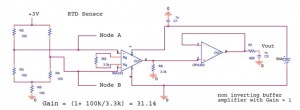

Per cominciare dobbiamo determinare il segnale di ingresso. In questo esempio di design, sarà utilizzato un sensore RTD (sensore di temperatura a resistenza) in configurazione a ponte di Wheatstone. L’obiettivo di questo circuito è misurare la temperatura nella gamma 0-70 °C, e il nostro ingresso sarà la differenza di potenziale tra il nodo A e il nodo B (Fig. 3).

La resistenza RTD varia da 100Ω a 127Ω che rappresenta 0-70 °C come range di temperatura. Differenza di tensione varia da 0 V a 91,94 mV, a passi di 3,74 mV per aumento 1Ω.

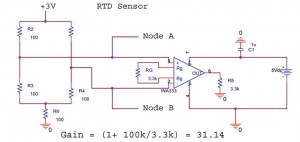

Il passo successivo è quello di progettare un circuito in grado di rilevare la differenza di potenziale in uscita tra il nodo A e il nodo B. INA333 (amplificatore di strumentazione) sarà utilizzato per questa operazione (nulla vieta di utilizzare un operazionale equivalente); è un tipo di amplificatore differenziale che non richiede adattamento di impedenza in ingresso attraverso due buffer.

Dall’analisi DC la massima differenza di tensione tra due nodi è 91.94 mV, per cui al fine di aumentare la risoluzione del rapporto segnale-rumore (SNR), progettiamo il circuito di amplificazione con guadagno di circa 30 (Fig. 4) per far si che la tensione corrisponda a un ADC in uso (esempio).

Dopo lo stadio di amplificazione di condizionamento, il segnale deve essere filtrato e ottimizzato. Il design del filtro RC è determinato seguendo alcuni parametri di lavoro: tempo di acquisizione, capacità di ingresso dell’ADC e la gamma di tensione in ingresso di fondo scala (Fig. 5).

La capacità è impostata per essere almeno più grande di 20 volte rispetto a quella di ingresso dell’ADC. Utilizzando un condensatore con capacità di 1 nF, la resistenza esterna equivalente deve essere almeno maggiore di 398 ohm, quindi un opportuno amplificatore-buffer dovrà essere scelto. OPA363 di Texas Instruments (per esempio) può essere ideale come amplificatore-buffer dovuto al basso rapporto di reiezione di modo comune (CMRR) e ottimizzato per essere utilizzato come un driver per capacità di ingresso dell’ADC (Fig. 4).

Conversione ADC

Il collegamento del circuito digitale con il sensore può essere fatto solo se i sensori sono intrinsecamente digitali. Tuttavia, quando i segnali analogici sono coinvolti nel progetto, l’interfaccia diventa molto più complessa. In questo caso è necessario un modo per tradurre i segnali analogici in forma digitale con un ADC.

Tipicamente, un ADC (Fig. 6) è un dispositivo elettronico che converte una tensione analogica di ingresso o corrente in un numero digitale proporzionale alla grandezza della tensione o corrente.

Il numero dei bit di uscita di un ADC non specifica completamente il suo comportamento. Convertitori reali A/D possono differire dal comportamento ideale in molti modi. Tutti gli ADC soffrono di errori di non linearità causati dalle loro imperfezioni fisiche che permettono di deviare dalla loro funzione lineare (o qualche altra funzione, nel caso di un ADC volutamente non lineare) rispetto all’ingresso. Questi errori possono a volte essere mitigati dalla calibrazione, o impediti da test. Parametri importanti sono le non-linearità, integrali (INL) e differenziali (DNL). Questi riducono la gamma dinamica dei segnali analogici che possono essere digitalizzati dall’ADC, riducendo anche la sua risoluzione effettiva.

Il costo di un ADC è proporzionale ai seguenti parametri: precisione, il numero di bit e stabilità.

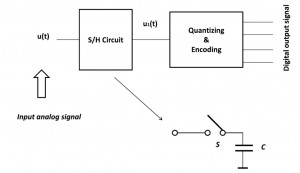

L’estrapolazione di nuovi valori digitali del segnale di ingresso verrà effettuato in accordo a un rate di campionamento. Questo rate viene chiamato frequenza di campionamento o più dettagliatamente frequenza di campionamento del convertitore (Sample & Hold, Fig.7).

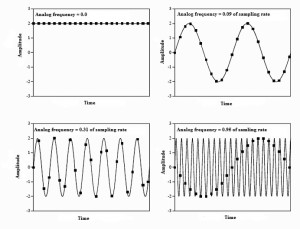

Per convertire un segnale analogico in forma digitale deve essere prima a banda limitata e poi campionato. Teoricamente la frequenza massima che può essere utile è la metà della frequenza di campionamento. I segnali campionati sono rappresentati da multipli di periodo di campionamento T, come s(nT), dove n è un numero intero.

Il teorema del campionamento indica che un segnale analogico può essere correttamente campionato, solo se la sua frequenza massima non è superiore alla metà della frequenza di campionamento. Se le componenti di frequenza sono al di sopra di questo limite, saranno aliasate (Alias).

Il DS1843 di Maxim è un esempio di circuito sample-and-hold (Fig. 8), utile per catturare segnali veloci. Esso comprende un differenziale, stage di input ad alta velocità di switching a condensatore commutato, circuito nulling di offset e un buffer di uscita. Il DS1843 è ottimizzato per l’utilizzo in sistemi di trasmissione su linea ottica (OLT) per misurazione RSSI burst-mode in combinazione con un resistore di rilevamento esterno.

Leggi gli articoli precedenti

DAQ (parte 1) – Sistemi di acquisizione dati: generalità di progettazione

Maurizio Di Paolo Emilio

Contenuti correlati

-

La digitalizzazione delle piccole aziende italiane: la ricerca di reichelt elektronik

reichelt elektronik, in collaborazione con la società di ricerca OnePoll, ha analizzato un campione di 250 aziende di piccole dimensioni, che contano tra i 2 ed i 50 dipendenti, presenti sul territorio italiano, per fare il punto...

-

congatec e S.I.E annunciano servizi di co-creazione per la digitalizzazione della sanità

congatec e System Industrie Electronic (S.I.E), azienda specializzata nella progettazione e integrazione di sistemi, produzione in volumi e assemblaggio di piattaforme OEM per il settore medicale, hanno ufficialmente presentato i loro servizi di co-creazione (cioè il processo...

-

Plug & Produce

La digitalizzazione della produzione si diffonde sempre di più. Mentre si affermano tendenze tecnologiche come SPE ed Ethernet APL, i livelli di automazione iniziano a convergere. In questo contesto, componenti d’interconnessione elettrici di grande affidabilità e dalle...

-

La digitalizzazione riduce gli errori ed elimina gli scarti per le New Product Introductions

Grazie all’adozione di strategie smart orientate alla produzione, le divisioni di progettazione e di produzione di Egicon sono in grado di verificare immediatamente che un progetto sia realizzabile, che il piano di produzione sia aggiornato e sincronizzato,...

-

Analog Devices: soluzione DAQ μModule di precisione e ad alta velocità

La soluzione per l’acquisizione dati (DAQ) µModule a 16 bit e 15 MSPS di Analog Devices permette la digitalizzazione di segnali transitori veloci nelle applicazioni di power analysis e per l’abilitazione del loop di controllo digitale a...

-

Da Acceed un computer DAQ per applicazioni edge

MCM-204 è un computer disponibile da Acceed per applicazioni di data recording (DAQ) a livello edge. Si tratta di un prodotto estremamente compatto e dotato di quattro ingressi analogici ad alta risoluzione e uscite digitali dedicate che...

-

Nel cuore della digitalizzazione

Marco Costa, regional manager for cloud protection and licensing activity di Thales illustra i vantaggi che una politica di software licensing può avere in tutti i settori Gemalto è oggi una delle sette divisioni globali di Thales, società che opera nei...

-

Nuove attività data-driven per i CFO di domani al CFO Summit 2019 di BI

Più di un CFO su due in Italia ritiene che la propria organizzazione debba adeguare o rinnovare il proprio modello di business, per stare al passo con le forti pressioni derivanti dall’innovazione tecnologica. E’ quanto emerge dalla...

-

Murata introduce nuovi convertitori DC-DC da 600 W in formato ¼ brick

Murata Power Solutions ha annunciato nuovi convertitori DC-DC da 600 W in formato ¼ brick basati su un processore ARM a 32 bit. Queste nuove famiglie sono conformi alle specifiche DOSA e supportano i più recenti comandi...

-

Cisco e TIM insieme per accelerare la digitalizzazione dell’Italia

Cisco e TIM hanno scelto il Mobile World Congress di Barcellona, per annunciare la firma di un importante protocollo di intesa che ha l’obiettivo di accelerare la digitalizzazione dell’Italia. Con questo accordo, le due aziende si impegnano...