Come e perché effettuare il reset da remoto delle memorie flash seriali

Paul Hill

Director – Product Marketing

(Adesto Technologies)

Nella progettazione di sistemi embedded la stabilità di un progetto è un elemento critico e il reset rappresenta un mezzo efficace per la correzione degli errori di runtime (ovvero che si manifestano durante l’esecuzione). Sfortunatamente i produttori di memorie sono impegnati a sviluppare package sempre più piccoli che quindi non prevedono il supporto di un pin di reset hardware dedicato. Ciò comunque non rappresenta più un problema per i dispositivi flash seriali conformi al nuovo standard JESD252 di JEDEC il quale definisce un meccanismo di reset che non richiede la presenza di un pin dedicato.

Gli errori transitori che si manifestano nei sistemi elettronici sono imputabili a numerosi fattori, tra cui problemi di integrità dei segnali e radiazioni di fondo (background noise) che possono alterare il contenuto della memoria, provocando errori di programmazione e nei dati. Per ovviare a malfunzionamenti di questo tipo, si potrebbe considerare in prima istanza la possibilità di spegnere e riaccendere il sistema. Se questa soluzione può risultare efficace, anche se un po’ fastidiosa, per i dispositivi consumer, rappresenta invece un problema di una certa entità per i sistemi embedded e i nodi IoT. Apparati di questo tipo devono operare su base continua e con tempi di fermo (downtime) minimi. Spesso sono dislocato in luoghi di difficile accessibilità, per cui devono essere in grado di effettuare il ripristino in presenza di eventuali malfunzionamenti senza dover ricorrere all’intervento di un operatore. Anche se sistemi di questo tipo di solito integrano meccanismi di auto-diagnostica, come ad esempio WDT (Watch-Dog Timer), al fine di rilevare eventuali malfunzionamenti e intraprendere le necessarie azioni correttive, spesso tale misura non risulta sufficiente.

I progettisti, ovviamente, assicurano che all’accensione i dispositivi si trovino in uno stato noto. In ogni caso, un soft reset può anche rientrare in una strategia di correzione dell’errore, per cui è importante che il sistema nel suo complesso sia in grado di effettuare il reset di componenti e sottosistemi.

Il reset di una memoria flash seriale

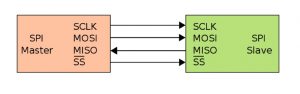

Nei sistemi embedded, l’interfaccia SPI (Serial Peripheral Interface) è ampiamente diffusa per collegare i microcontrollori a periferiche e dispositivi di memoria. In particolare, essa è spesso utilizzata per le flash seriali di tipo NOR che memorizzano il codice eseguibile.

Le specifiche SPI originali prevedevano un singolo filo per la trasmissione dati (data wire) in ciascuna direzione. La velocità, quindi, non era sufficiente per supportare l’esecuzione di codice ad alte prestazioni direttamente dalla memoria seriale. Per questo motivo il codice doveva essere copiato sulla SRAM prima di essere eseguito, con conseguente aumento dei tempi di avviamento (start-up) e dei costi del sistema.

Al fine di aumentare l’ampiezza di banda rispetto a quella prevista dalle specifiche SPI originali, è possibile utilizzare quattro oppure otto segnali di dati (data signal), in modo da poter trasferire un numero maggiore di bit di dati per ogni ciclo di clock.

Queste interfacce xSPI (expanded SPI) sono definite dallo standard JESD251 di JEDEC. Le moderne memorie xSPI ottali (ovvero con 8 I/O) come quelle della linea EcoXiP di Adesto, garantiscono le prestazioni richieste per eseguire il codice direttamente dalla memoria seriale, tecnica questa conosciuta come XiP (eXecute in Place – esecuzione sul posto). Un approccio di questo tipo, oltre a garantire maggiori prestazioni e a supportare la funzionalità di “instant-on” (ovvero di accesso rapido al sistema), consente anche di minimizzare i consumi di potenza. Inoltre è possibile ridurre la quantità di SRAM richiesta e, di conseguenza i costi del sistema.

Nel caso si verifichi un guasto nel sistema, potrebbe essere necessario effettuare il reset della memoria seriale nell’ambito del processo di ripristino. Come ricordato all’inizio, a causa delle pressioni esercitate sui produttori per realizzare package sempre più piccoli (ed economici) con un numero ridotto di pin, molte memorie seriali non prevedono un pin di reset o, nel caso sia presente, esso è multiplato con un’altra funzione, rendendone difficoltoso l’utilizzo. Il nuovo protocollo per il reset delle memorie flash seriali messo a punto da JEDEC e definito nello standard JESD252 consente il controllo della funzione di reset senza ricorrere a un pin dedicato.

Al posto del pin di reset, lo standard JESD252 utilizza i segnali dell’interfaccia SPI (clock, chip select e serial data) per trasmette una sequenza che forza il reset del dispositivo target. Nel corso di una sequenza di reset il segnale di clock viene mantenuto nello stato logico basso per distinguere la transazione di reset da un comando SPI normale e impedire l’invio di qualsiasi comando SPI, utilizzando il segnale di “chip select” come clock per il dispositivo target. Una sequenza specificata di transizioni è trasferita sul pin di dati al fine di impedire reset erronei provocati dal rumore.

Adesto ha già fornito le prime memorie flash di tipo NOR con interfaccia seriale in grado di supportare lo standard JESD252 al quale risultano conformi anche le memorie della linea EcoXiP dotate di interfaccia SPI ottale per garantire maggiori prestazioni rispetto a quelle offerte da analoghi dispositivi con interfaccia quadrupla. La possibilità di effettuare i caricamenti delle istruzioni in maniera sequenziale senza la necessità di inviare un indirizzo per ogni lettura contribuisce a incrementare le prestazioni in termini di esecuzione. La serie EcoXiP prevede anche funzionalità che permettono da un lato di ridurre I consumi di potenza e dall’altro di assicurare un maggior livello di sicurezza.

Realizzare progetti migliori

Grazie alla funzionalità XiP è possibile ottenere le prestazioni desiderate a fronte di una riduzione sia dei consumi sia dei costi. Anche se XiP richiede un’interfaccia di memoria compatibile sul microcontrollore, un numero sempre crescente di produttori sta aggiungendo questo tipo di supporto ai propri dispositivi. L’adozione di memorie flash seriali che supportano il protocollo di reset seriale conforme a JESD252 permette di realizzare prodotti più stabili e affidabili che soddisfano quindi “in toto” le aspettative degli utilizzatori.

Contenuti correlati

-

Uno sguardo all’evoluzione delle Flash NOR

Le memorie Flash NOR esterne da 1,2 V di ultima generazione assicurano un maggiore risparmio energetico nei prodotti basati su SoC realizzati con geometrie inferiori a 10 nm Leggi l’articolo completo su EO 515

-

Veicoli definiti dal software: il ruolo delle flash

I progressi nel settore delle memorie flash supportano l’evoluzione dei veicoli definiti dal software Leggi l’articolo completo su EO 513

-

NAND per il settore automotive

Un’analisi delle differenze tra le memorie flash per il settore automotive e gli analoghi dispositivi destinati al mondo consumer Leggi l’articolo completo su EO 510

-

KIOXIA amplia la gamma di prodotti con memoria flash integrata

KIOXIA Europe ha annunciato il campionamento della più recente generazione dei suoi prodotti con memoria flash incorporata conformi con la specifica JEDEC e-MMC ver. 5.1 per applicazioni consumer. I nuovi prodotti sono disponibili con capacità di 64...

-

Winbond introduce una nuova memoria Flash NOR SPI a 1,2 V da 64 Mb

W25Q64NE è la sigla di una nuova memoria Flash NOR di Winbond Electronics. Questo componente della linea SpiFlash a 1,2 V ha una densità di 64 Mb ed è dotata della funzionalità di risparmio energetico attivo. Queste...

-

La nuova flash NOR da 512 Mb a 1,8V di Winbond Electronics

La nuova W25Q512NW di Winbond Electronics è una memoria flash NOR monolitica da 512 Mb a 1,8 V con interfaccia SPI. Questo componente supporta operazioni in modalità standard/duale/quadrupla con clock fino a 166 Mhz e assicura la...

-

Memorie Flash embedded conformi alla versione 5.1 dello standard e-MMC da Toshiba

Toshiba Memory Europe ha annunciato quattro nuovi prodotti conformi alla versione 5.1 dello standard JEDEC e-MMC (MultiMediaCard Embedded) per applicazioni consumer. Le nuova memorie Flash integrano in un unico package una memoria Flash 3D BiCS FLASH di...

-

Cypress: nuove memorie Flash per applicazioni automotive, industriali e IoT

Cypress Semiconductor ha ampliato la sua offerta di memorie Flash NOR con modelli con densità di 64 Mb e 128 Mb. I dispositivi FL-L offrono un basso il consumo di energia, sono qualificati AEC-Q100 per applicazioni automotive,...

-

JEDEC: JESD209-4 Low Power Double Data Rate per Mobile

JEDEC Solid State Technology Association ha annunciato la pubblicazione di JESD209-4 Low Power Double Data Rate 4 (LPDDR4), destinato ad aumentare la velocità di memoria e di efficienza per i dispositivi di mobile computing. Caratteristiche chiave includono:...

-

I nuovi accoppiatori a fototriac di Toshiba

Toshiba Electronics Europe ha lanciato due nuovi fotoaccoppiatori con uscita a triac che forniscono un isolamento rinforzato e basse correnti di innesco del LED, non superiori a 3 mA. Questa riduzione delle correnti di trigger permette ai...