TECH-FOCUS

I3C

32

- ELETTRONICA OGGI 467 - GENNAIO/FEBBRAIO 2018

NXP implementerà le nuove IP Silvaco in tutti

i nuovi chip NXP che avranno bisogno delle

interfacce I3C.

Synopsys

ha aggiunto nel suo DesignWare

ARC Data Fusion IP Subsystem basato sul

processore ARC EM9D una suite di periferi-

che che comprende un’interfaccia I3C che

si affianca alla I2C, un PDM (Pulse Density

Modulator), una MIPI Camera Control Interface

(CCI) e un processore audio di riconoscimento

vocale. In opzione c’è anche il modulo ARC

CryptoPack che contiene le funzionali-

tà crittografiche con gli algoritmi AES,

SHA-256, RSA e ECC. Questo sottosi-

stema consente di realizzare sistemi

DSP comprensivi dell’acquisizione dei

comandi vocali ideali per creare nodi

IoT multi-funzione. Synopsys e Brite

Semiconductor di Shanghai ne hanno

recentemente avviato l’integrazione

sul silicio nella forma di ASIC insieme

alle interfacce I3C e USB utilizzando i

processi in geometria di riga da 55 nm

disponibili nelle fonderie SMIC della

stessa Shanghai.

VIP per I3C

Avery Design Systems, Cadence

e

Synopsys

hanno già preparato i

Verification IP (VIP) per le interfacce

I3C ossia i moduli di verifica riutilizza-

bili che consentono di testare rapida-

mente le funzionalità dei bus I3C ana-

lizzando il traffico e la correttezza dei

protocolli. Il VIP I3C-Xactor di Avery Design

Systems supporta le specifiche dei sensori

MIPI I3C nelle due modalità master e slave non-

ché le specifiche I2C 4.0 e SMBus 2.0. Si può

programmare con i linguaggi SystemVerilog e

VHDL che consentono di implementare veri-

fiche sull’arbitraggio dei bus e sull’adatta-

mento dinamico del clock nelle diverse velo-

cità consentite. Cadence ha aggiunto alla sua

ampia famiglia di Verification IP per i proto-

colli MIPI anche i nuovi MIPI I3C Simulation

VIP pensati per la veri-

fica delle interfacce I3C

nelle modalità SDR e HDR

e in tutte le funzionalità

dinamiche di arbitraggio

e indirizzamento. Questi

tool sono caratterizza-

ti da un’ampia scelta di

linguaggi di configurazio-

ne fra cui SystemVerilog,

Verilog, VHDL e C/C++.

Synopsys VC Verification

IP per MIPI I3C permette

di sviluppare piattaforme

di verifica sulle interfacce

I3C e I2C nelle modalità

multi-master e multi-slave

esaminando l’allocazio-

ne dinamica degli indi-

rizzamenti e la completa

gestione degli interrupt.

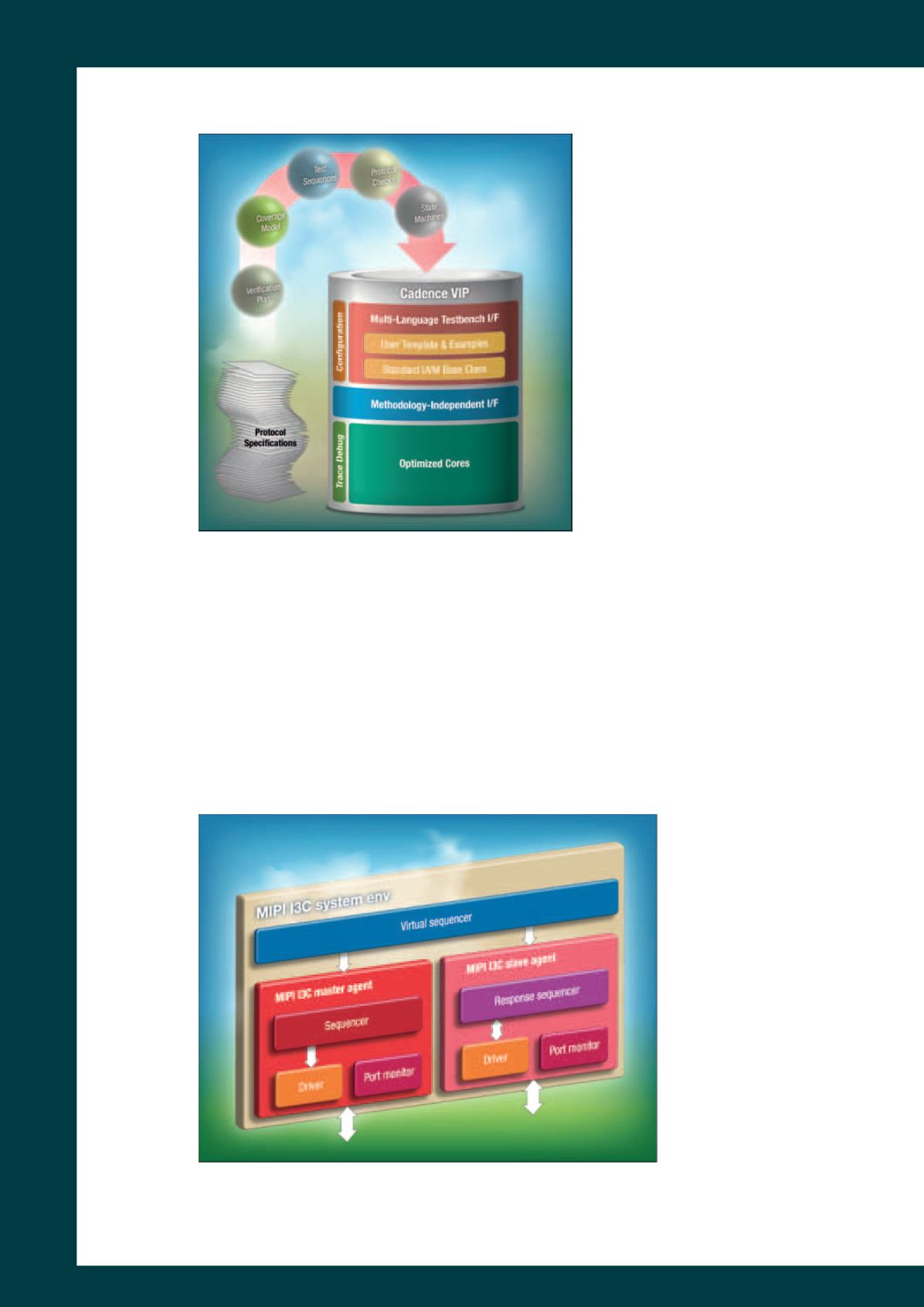

Fig. 7 – Synopsys VC Verification IP consente la verifica sulle interfacce I3C in tutte le

modalità operativemulti-master emulti-slave

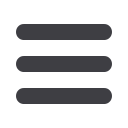

Fig. 6 – I nuovi MIPI I3C Simulation VIP di Cadence sono configurabili in

SystemVerilog, Verilog, VHDL e C/C++