TECH INSIGHT

NEWS/TECHNOLOGIES

le attività di elaborazione delle

reti neurali. I sistemi di visione

automotive basati su teleca-

mera, i droni e i sistemi di si-

curezza implicano fondamen-

talmente due tipi elaborazione

ottimizzata per le immagini. In

primo luogo, il miglioramento

dell’input dalla fotocamera tra-

mite algoritmi di calcolo tradi-

zionali per fotografia/imaging.

In secondo luogo, il rileva-

mento e il riconoscimento de-

gli oggetti tramite algoritmi di

riconoscimento basati su rete

neurale.

Le soluzioni di accelerazione

per reti neurali esistenti sono

elementi hardware collegati al

DSP di imaging in cui il codi-

ce di rete neurale è diviso tra

l’esecuzione di alcuni livelli di

rete e l’alleggerimento dell’ac-

celeratore dai livelli convoluzionali. Questa combinazione è inefficiente e consuma energia inutilmente. Configu-

rato come DSP dedicato e ottimizzato per le reti neurali, Vision C5 accelera non solo le funzioni di convoluzione

ma anche i livelli di elaborazione della rete neurale (convoluzione, connessione, condivisione e normalizza-

zione). Questo alleggerisce il DSP principale di visione/imaging permettendogli di eseguire le applicazioni di

ottimizzazione dell’immagine in modo indipendente, mentre il DSP Vision C5 esegue le attività di inferenza.

Minimizzando il trasferimento di dati tra il DSP per reti neurali e il DSP principale di visione/imaging, Vision C5

mette a disposizione una soluzione a consumo ridotto all’altezza degli acceleratori per reti neurali. Inoltre esso

offre anche un semplice modello di programmazione a singolo processore per reti neurali.

Caratteristiche e prestazioni

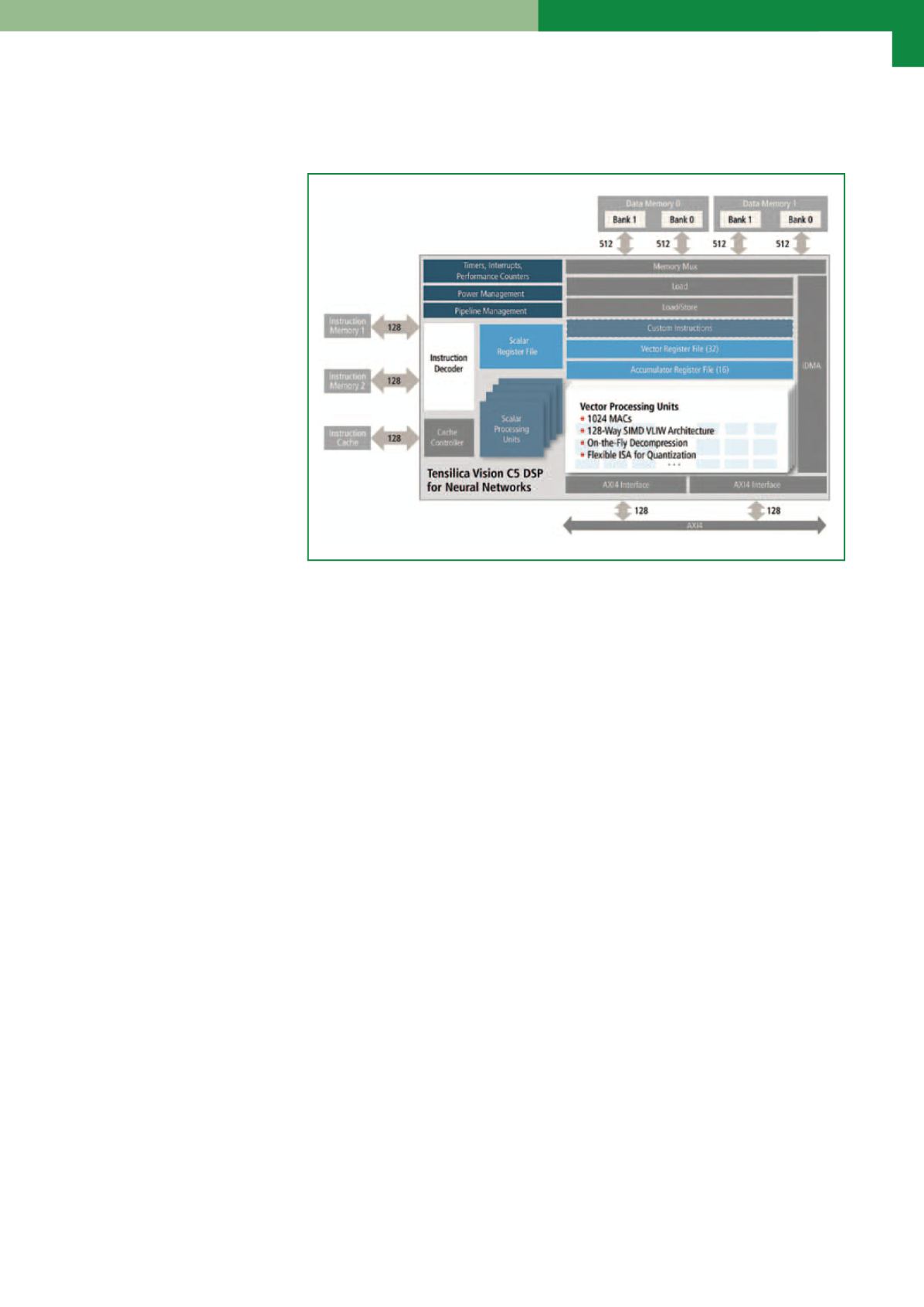

Il DSP Vision C5 integra delle prestazioni per reti neurali ai vertici della categoria in un engine autonomo carat-

terizzato da:

• Capacità di calcolo di 1TMAC/s (throughput 4 volte superiore rispetto al DSP Vision P6) in meno di 1 mm

2

di

silicio per un elevato throughput di calcolo su kernel di apprendimento profondo.

• 1024 MAC a 8-bit o 512 MAC a 16 bit per garantire elevate prestazioni con risoluzioni sia a 8 bit sia a 16 bit.

• Architettura VLIW SIMD con 128 vie, SIMD a 8 bit o SIMD a 16 bit a 64 vie.

• Configurazione per progetti multi-core che consente di ottenere prestazioni dell’ordine dei multi-teraMAC/s

in uno spazio ridotto.

• iDMA integrato e interfaccia AXI4.

• Utilizzo dello stesso collaudato set di strumenti software dei DSP Vision P5 e P6.

• Rispetto alle GPU concorrenti, DSP Vision C5 è in grado di eseguire il benchmark AlexNet CNN fino a 6 volte

più velocemente e il benchmark Inception V3 CNN fino a 9 volte più velocemente.

DSP Vision C5 supporta kernel con dimensioni, profondità e input variabili. Esso gestisce anche diverse tec-

niche di compressione/decompressione dei coefficienti, e permette di implementare il supporto di nuovi layer

man mano che evolvono. Al contrario, gli acceleratori hardware forniscono una soluzione meno flessibile a

causa della limitata riprogrammabilità. DSP Vision C5 è inoltre corredato dal set di tool di mappatura per reti

neurali Cadence. Questi strumenti permettono di mappare qualsiasi rete neurale addestrata con tool quali Caffe

e TensorFlow per ottenere un codice eseguibile e altamente ottimizzato per il DSP Vision C5, che beneficia di

una serie completa di funzioni di libreria per reti neurali ottimizzate.

25

- ELETTRONICA OGGI 463 - GIUGNO/LUGLIO 2017

Cadence è un DSP sotto forma di IP per reti neurali destinata alle applicazioni automotive e di sorve-

glianza, ai droni e ai dispositivi mobili