TECH INSIGHT

VISIONE ARTIFICIALE

20

- ELETTRONICA OGGI 463 - GIUGNO/LUGLIO 2017

La progettazione dei sistemi

di visione basati

sulla visione artificiale

Parte 4 –

Kit di visione

In questa parte viene descritta la realizzazione di un sistema di visione

embedded utilizzando un kit di visione realizzato “ad hoc”

A cura di Xilinx

G

li articoli precedenti di questa serie hanno descritto le procedure di selezione dei sensori, un sistema di

visione embedded e il modo in cui i blocchi funzionali possono essere realizzati all’interno di un sistema

che combina un processore ad alte prestazioni e una matrice FPGA.

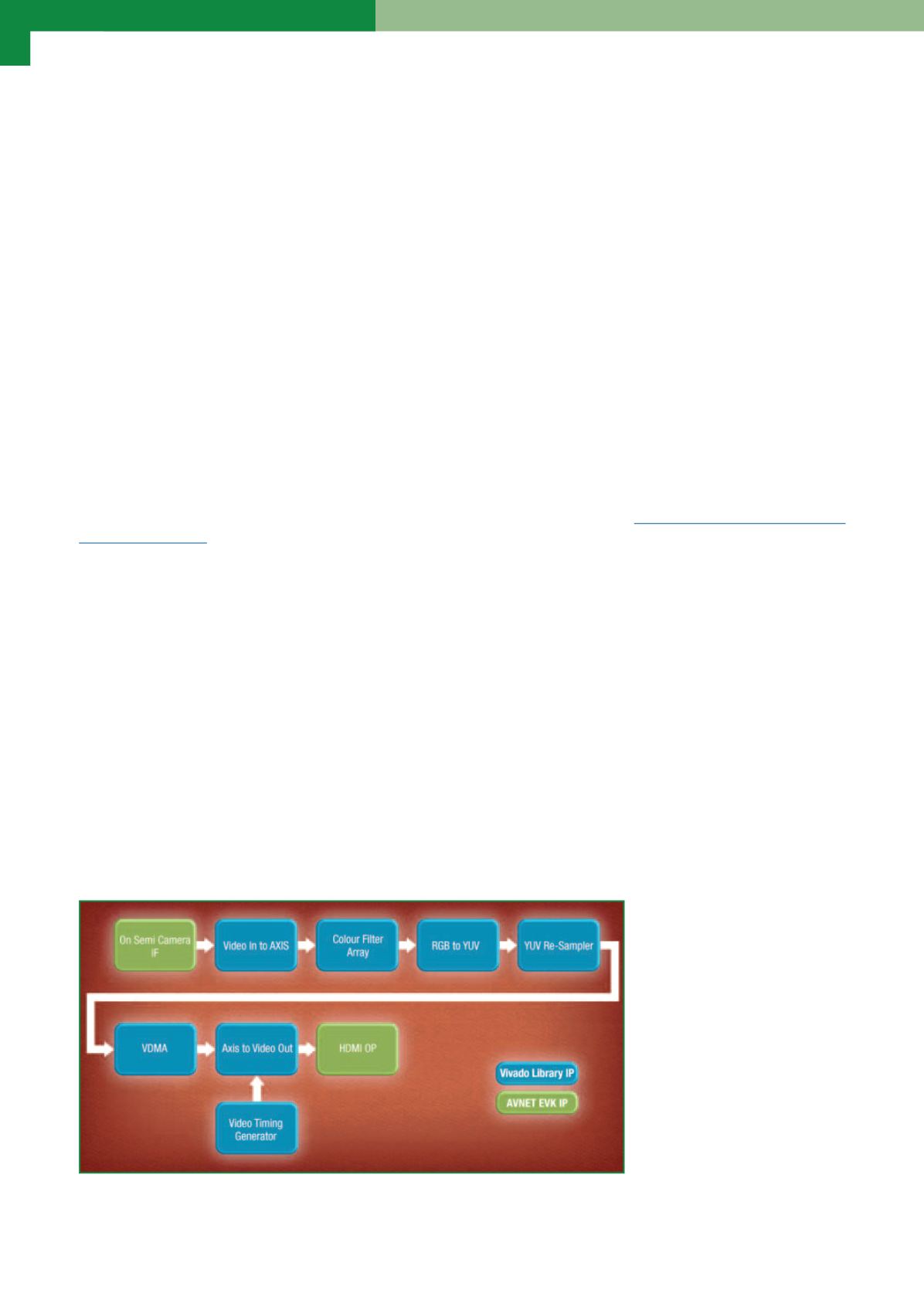

Questo articolo illustra come costruire un sistema di visione embedded usando il

Kit di Visione Embedded (EVK)

MicroZed di Avnet

, che contiene il sensore di immagini CMOS Python 1300C di On Semiconductor e il SoC pro-

grammabile Zynq 7020 di Xilinx.

Python 1300C è un sensore di colori con 1280 pixel x 1024 linee, configurato attraverso un’interfaccia SPI, la

sua uscita serializzata supporta velocità elevate dei fotogrammi, mentre l’EVK fornisce una connessione HDMI

ad uno schermo.

Il dispositivo Zynq 7020 realizza le funzionalità del sistema, usando una matrice FPGA (in logica programmabi-

le, o PL), per creare l’interfaccia del dispositivo e la catena di elaborazione delle immagini. Due core ARM A9

alimentano il Sistema di Elaborazione (PS) di Zynq, che può essere usato per la supervisione del sistema e, se

richiesto, per l’estensione della catena di elaborazione delle immagini.

La realizzazione dell’hardware

In questo caso vengono utilizzati due tool di sviluppo dei SoC: Xilinx Vivado 2015.4 e Xilinx SDK 2015.4. Vivado

è usato per realizzare l’interfaccia del dispositivo e la catena di elaborazione delle immagini, oltre che per confi-

gurare il PS all’interno di Zynq e per stabilire comunicazioni da PS a PL mappate in memoria per configurare l’IP

nella catena di elaborazione delle immagini in base alle dimensioni delle immagini, alle velocità dei fotogrammi

e alle operazioni richieste. Questo è ottenuto usando l’interconnessione AXI con funzione generica situata fra il

PS e la PL, con il PS in qualità di master.

Il tool Vivado è anche usato per collocare la memoria DDR all’interno della catena di elaborazione delle immagi-

ni di modo tale che il proces-

sore possa accedervi se ne-

cessario. Ciò può essere fatto

usando

l’interconnessione

AXI fra la PL e il PS, in cui la

PL è il master.

Questo sistema dimostrati-

vo invia l’immagine a uno

schermo su una connessione

HDMI, usando il modulo IP di

interfaccia verso il disposi-

tivo per il Python 1300C, e il

modulo IP fra la connessione

HDMI e l’uscita per interfac-

ciarsi con il dispositivo HDMI

in uscita sull’EVK. Questi mo-

duli IP sono inclusi nel kit.

Fig. 1 – Funzioni eseguite dalla catena di elaborazione delle immagini