TECH INSIGHT

VISIONE ARTIFICIALE

21

- ELETTRONICA OGGI 463 - GIUGNO/LUGLIO 2017

La catena di elaborazione delle

immagini si interfaccia al Python 1330C ed esegue le funzioni mostrate in figu-

ra 1. Tutti i core IP usati sono contenuti all’interno della libreria IP standard di Vivado per l’Elaborazione delle

Immagini, a eccezione del Python 1300C e dei core IP HDMI. Il nome dei core e le funzioni che eseguono sono

elencati di seguito:

•

Video In to AXIS

: converte il video parallelo, e le sincronizzazioni in orizzontale e in verticale, dall’Interfaccia

IP Python verso un flusso AXI per l’interfacciamento con i core IP di elaborazione delle immagini.

•

Colour filter array interpolation

: consente di assegnare a ciascun pixel un valore RGB usando l’informazione

proveniente dallo schema di Bayer relativo ai pixel di ingresso.

•

RGB to YCRCB colour-space convertor

: converte lo spazio dei colori per assicurare che il segnale in uscita

sia nel formato preferito dal driver HDMI.

•

Chroma resampler

: riscala l’YUV dal formato 4:4:4 a quello 4:2:2.

•

AXI VDMA

: configura un Video DMA per trasferire i fotogrammi delle immagini alla memoria DDR del PS.

•

AXI VDMA

: configura lo stesso Video DMA per leggere i fotogrammi delle immagini alla memoria DDR del PS.

•

AXIS to video out

: converte il flusso AXI nuovamente al formato parallelo.

•

Video timing controller

: fornisce un generatore di riferimento temporale per la temporizzazione del video in

uscita.

Inoltre, sono richiesti due moduli di interconnessioni AXI per assicurare che il sistema funzioni correttamente.

Uno è necessario per le interconnessioni AXI ad alte prestazioni, e l’altro per le Interconnessioni AXI con funzio-

ne generica, assieme ai blocchi di reset necessari per ciascuno dei domini di clock.

Le applicazioni di elaborazione delle immagini richiedono diversi domini di clock, e gran parte di essi possono

essere forniti usando i clock della matrice PL fornita dal PS all’interno del dispositivo Zynq. Questa applicazione

richiede i seguenti clock:

•

108MHz

: la velocità del clock dei pixel per un’immagine inviata in formato 1280 x 1024 a 60Hz.

•

75MHz

: per le interfacce AXI e AXI lite mappate in memoria.

•

150MHz

: per la catena di elaborazione delle immagini, anche nota come clock del Flusso AXI. Quest’ultimo

deve essere almeno pari alla velocità dei pixel. A frequenze superiori è opportuno avere del margine e ridurre

la memoria temporanea richiesta.

•

200MHz

: clock di riferimento verso il sensore Python 1300C.

Un clock wizard è usato per generare il clock da 108MHz dei pixel, dato che quest’ultimo deve essere impostato

in modo molto accurato. Mentre i clock a 75 MHz e a 150 MHz presentano qualche tolleranza quando sono impo-

stati in base ai clock della matrice PL, anche il clock da 200 MHz richiede un’accuratezza elevata. Diversamente

dal clock da 108 MHz, quest’ultimo può essere generato in modo accurato dai clock della matrice PS.

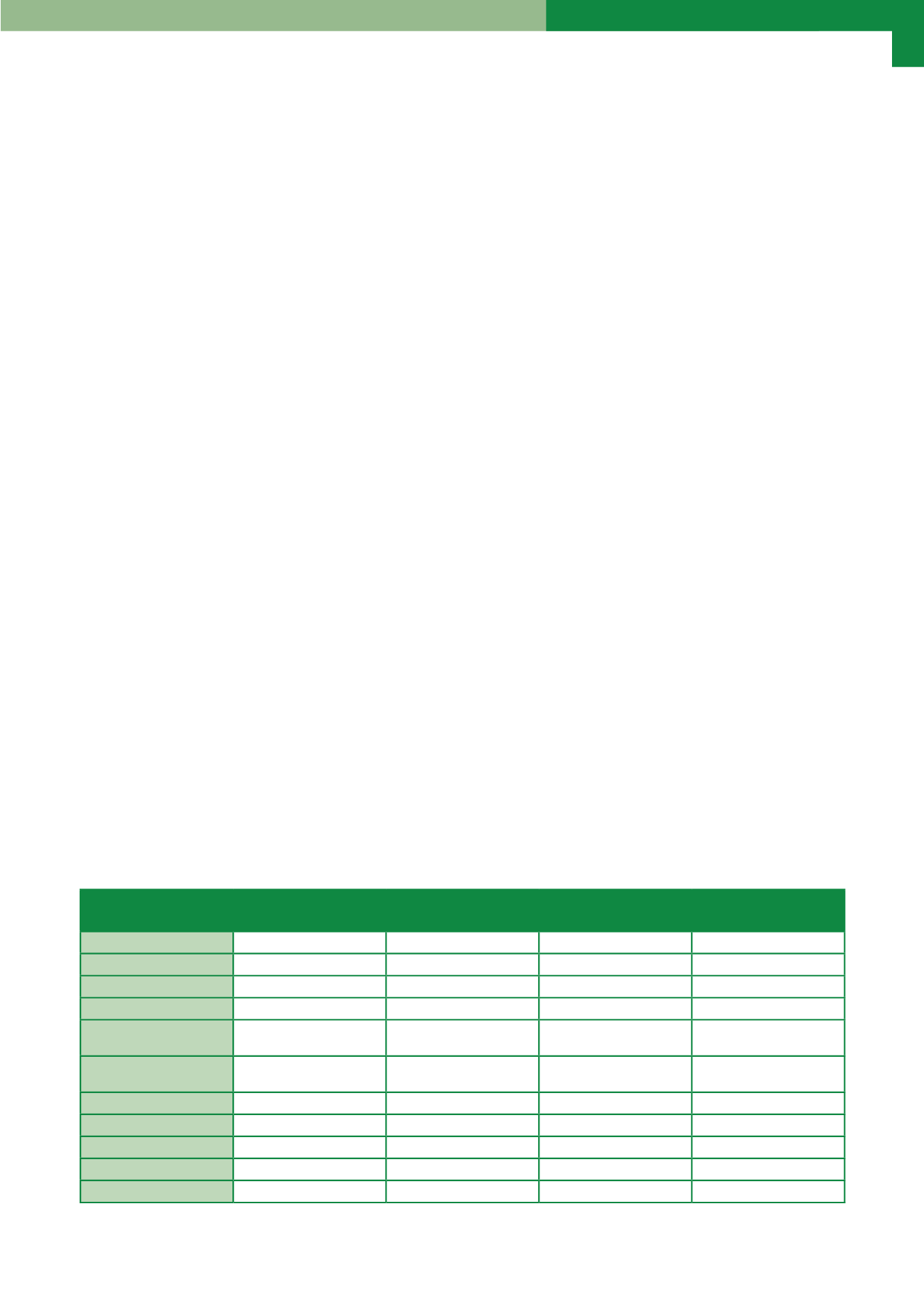

La tabella 1 descrive la struttura di temporizzazione dei moduli IP usati.

Tabella 1 – Struttura delle temporizzazioni

Modulo IP

AXI Lite / MM clock

Clock per il Flusso AXI

Clock dei Pixel

Ulteriori Clock

On Semi Python 1300C

NA

NA

108 MHz

200 MHz

On Semi SPI

75 MHz

NA

NA

NA

Video in to AXIS

NA

150 MHz

108 MHz

NA

Colour Filter Array interpo-

lation

75 MHz

150 MHz

NA

NA

RGB toYCRCB

Colour-Space Convertor

NA

150 MHz

NA

NA

Chroma Resampler

NA

150 MHz

NA

NA

AXI VDMA

75 MHz

150 MHz

NA

NA

AXIS to Video Out

NA

150 MHz

108 MHz

NA

Video Timing Controller

NA

NA

108 MHz

NA

HDMI OP

NA

NA

108 MHz

NA