TECH INSIGHT

21

- ELETTRONICA OGGI 457 - OTTOBRE 2016

INSTRUMENT CLUSTER IC

grafico di fascia alta in un cruscot-

to potrebbe ottenere un vantaggio

competitivo non indifferente. Questo

è il motivo per cui gli OEM e i princi-

pali fornitori (Tier 1) stanno svilup-

pando cruscotti di tipo ibrido con di-

splay grafici ad alte prestazioni che

in pratica abbinano i tradizionali in-

dicatori elettromeccanici su entram-

bi i lati dello schermo LCD TFT.

Il vantaggio di una configurazione

di questo tipo è dato dal fatto che

è possibile utilizzare schermi LCD

caratterizzati da dimensioni e risolu-

zioni molto inferiori rispetto a quelle

di un display completamente elet-

tronico presente sui veicoli di fascia

alta: ciò garantisce una sensibile ri-

duzione dei costi della BOM senza

per questo pregiudicare la possibili-

tà di visualizzare informazioni grafi-

che sofisticate in due o tre dimensio-

ni (2D/3D). Informazioni quali mappe

o assistenza al parcheggio possono

essere visualizzate in modo molto

chiaro in 2D o 3D su un display con una diagonale

pari a 3,5”.

L’altro elemento che contribuisce all’elevato costo

della BOM di un display completamente grafico è

rappresentato dal chipset. Per poter rispettare i se-

veri vincoli in termini di budget tipici dei veicoli di

fascia media è necessario ricorrere a una soluzione

su chip singolo per l’intero cruscotto. In questo caso

la migrazione verso il nodo tecnologico a 40 nm ha

rappresentato un’importante evoluzione. Questo

nodo tecnologico si è rivelato particolarmente im-

portante per l’industria dei semiconduttori: si trat-

ta di un processo economico, caratterizzato da una

resa elevata che permette di integrare più funziona-

lità (o in alternativa funzionalità migliori) in un chip

di dimensioni stabilite.

Il progetto di un cruscotto basato su un chip singolo

richiede un livello di integrazione particolarmente

spinto: esso può prevedere una CPU ad alte presta-

zioni, un controllore per LCD, Interfacce di comuni-

cazione operanti ad alta velocità oltre a numerose

periferiche. Inoltre, è necessaria una memoria RAM

ad alta velocità e di ampie dimensioni, poiché la ca-

pacità della memoria vincola la dimensioni e la ri-

soluzione del display che un sistema è in grado di

supportare.

L’importanza della memoria

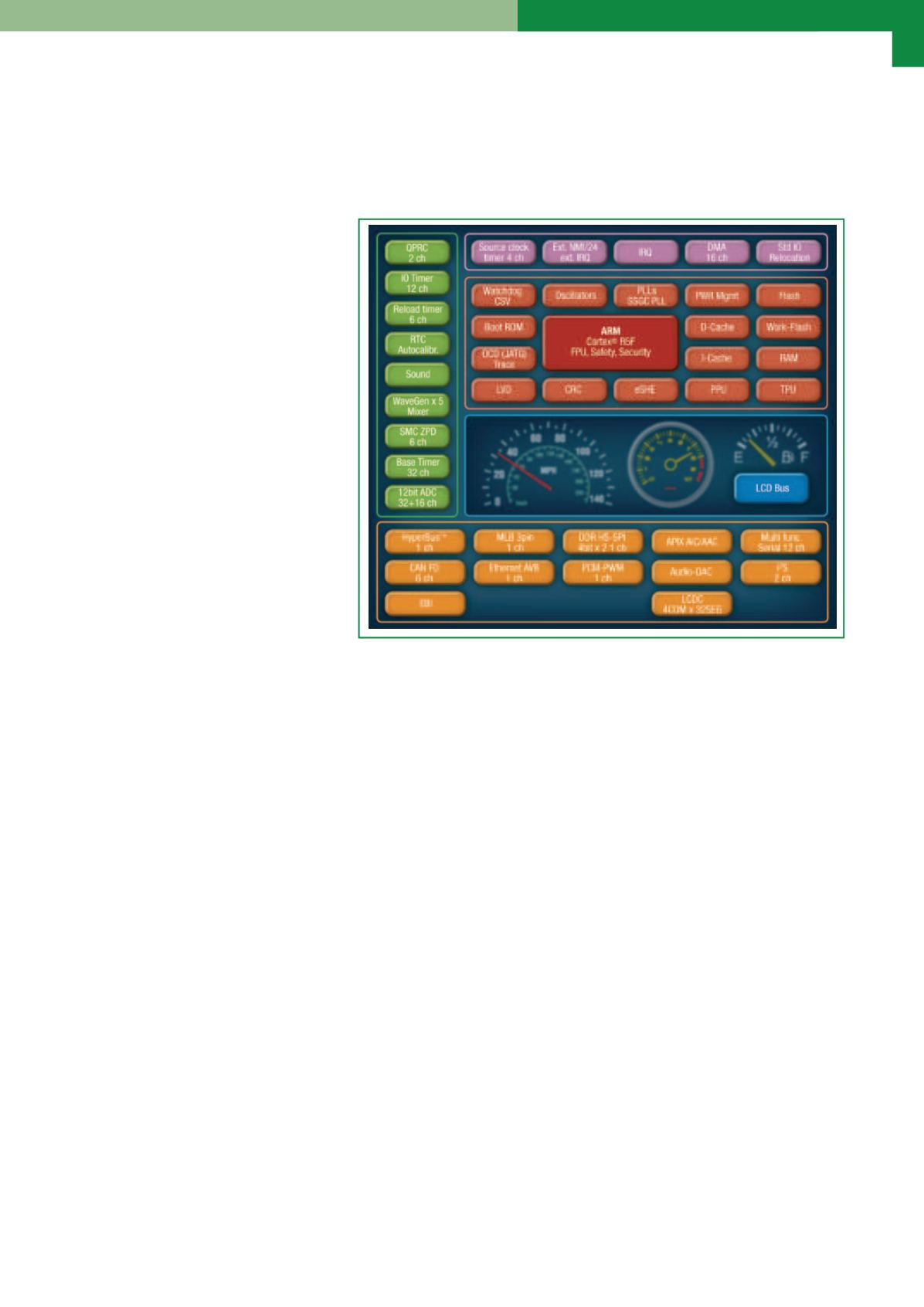

Un esempio delle potenzialità di integrazione offerte

dalla migrazione verso il nodo a 40 nm è rappresen-

tata dalla famiglia Traveo di Cypress Semiconductor,

formata da microcontrollori (MCU) per applicazioni

automotive. Attualmente i dispositivi della linea Tra-

veo sono equipaggiato con un massimo di 4 MB di

memoria flash embedded in grado di operare fino a

80 MHz senza cicli di attesa (wait state) unitamente a

384 kB di SRAM. Le nuove MCU S6J331X/S6J332X/

S6J333X/S6J334X integrano un core ARM Cortex-R5F

che prevede una cache dei dati e delle istruzioni ope-

rante a una frequenza massima di 240 MHz e garanti-

sce prestazioni di 400 DMIPS (Fig. 2).

Per molti progetti di cruscotti la dimensione della

memoria integrata nei microcontrollori della fami-

glia S6J33xx è sufficiente, consentendo in tal modo

di minimizzare costi, consumi di potenza e ingombri

(footprint). Nel caso le risorse di memoria disponi-

bili non fossero adeguate, le MCU della linea Traveo

prevedono un’interfaccia HyperBus che può essere

utilizzata per il collegamento con una memoria ester-

na. L’attuale generazione di memorie HyperRAM e

HyperFlash di Cypress sono caratterizzate da un’am-

piezza di banda di picco di 200MB/s (sull’interfaccia

HyperBus a 3V), in modo da consentire il funziona-

Fig. 2 – Schema a blocchi dei microcontrollori S6J331X/S6J332X/S6J333X/S6J334X della serie

Traveo di Cypress Semiconductor