DIGITAL

FPGA

42

- ELETTRONICA OGGI 451 - GENNAIO/FEBBRAIO 2016

di place&route di natura incrementale e l’impatto

sui tempi di compilazione è trascurabile. Per esegui-

re il retiming di un registro, la posizione del registro

è semplicemente trasferita in quella finale bilanciata

(ovvero con ritardi simmetrici) all’interno del per-

corso di routing dopo l’operazione di place&route

(si faccia riferimento alla Fig. 3). Si tratta di un van-

taggio di notevole entità nel caso di progetti che

prevedono bus dati di ampie dimensioni che, con le

architetture di tipo tradizionale, richiedono centina-

ia o migliaia di moduli ALM aggiuntivi per effettuare

il retiming, oltre all’esecuzione di numerose operazi-

oni di rerouting.

…e pipelining

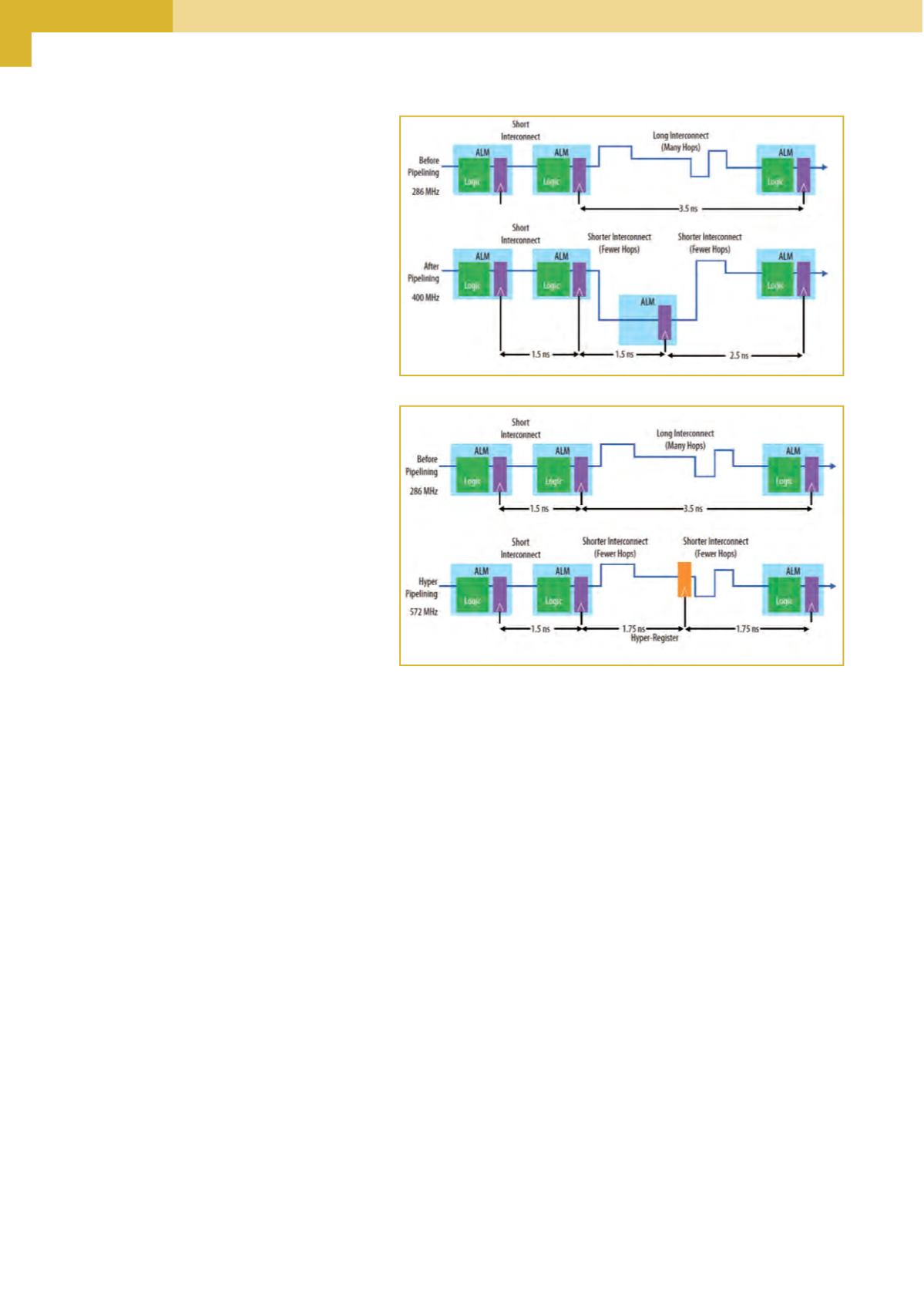

Il pipelining di tipo tradizionale ha gli stessi svan-

taggi del retiming e la mancanza di granularità dei

registri reduce l’efficacia di questa ottimizzazione. Si

tratta di un processo intrinsecamente iterativo po-

iché il numero degli stadi di pipeline richiesti e la

loro disposizione ottimale non sono noti nella fase

iniziale. Quindi è necessario ripetere più volte l’ope-

razione di place&route nel tentativo di convergere

a una soluzione di tipo pipelined (in cui sono stati

cioè inseriti gli opportuni registri) in grado di soddi-

sfare gli obbiettivi prefissati in termini di prestazioni.

La figura 4 riporta un semplice esempio di pipel-

ing in un’architettura di tipo tradizionale. Nell’architettura di

tipo HyperFlex, grazie agli Hiper-Register è possibile eseguire

l’operazione di pipeling senza alcun vincolo e senza ripercus-

sioni sulle dimensioni del progetto. In questo caso si parla di

Hyper-Pipelining. In molti casi, un progetto che prevede un

ricorso massiccio ai registri richiede un numero inferiore di

moduli ALM per la sua implementazione poichè non è neces-

sario ricorrere a moduli ALM solamente per poter utilizzare

i loro registri. Poichè l’operazione di pipeling non comporta

oneri aggiuntivi, è possibile fare un uso massiccio di questo

tecnica, soprattutto per la logica del percorso dati e di tipo feed

forward. Nella figura 5 è riportato un esempio di Hyper- Pipelin-

ing. Poiché il software per lo sviluppo con FPGA - Quartus II nel

caso dei dispositivi Altera – può eseguire automaticamente il

retiming della logica spostando i registri nell’interconnessione,

è necessario specificare solamente il numero di registri di pipe-

line richiesto all’ingresso di un dominio di clock o della logica

assegnata ai pin di una porzione del progetto. Il software quin-

di sposta i registri nel percorso di routing in base alle neces-

sità, dopo l’operazione di place&route, risolvendo in tal modo

il problema delle iterazioni multiple che è necessario effettuare

quando si esegue il pipelining nelle architetture tradizionali.

L’integrazione dei registri nella descrizione RTL semplifica la

parametrizzazione logica nel caso in cui le librerie di blocchi IP

(Intellectual property) supportano più di una frequenza di clock

(fMAX). I progetti sviluppati in modo tale da semplificare l’op-

erazione di pipelining sono quelli che trarranno sicuramente i

maggiori benefici dall’uso dell’architettura HyperFlex.

Ottimizzazione mirata

Una volta completati gli stadi di Hyper-Retiming e Hyper-Pipel-

ing è possibile che gli incrementi ottenuti in termini di prestazi-

oni in alcune sezioni del progetto possano evidenziare altri

“colli di bottiglia” che impediscono ulteriori miglioramenti. I

lunghi anelli di retroazione o una macchina a stati complessa

presenti in un circuito potrebbero essere alcune delle possibili

cause. L’ottimizzazione di una specifica sezione del progetto

deve quindi essere fatta con cognizione di causa. Un’operazi-

one di “Hyper-Optimization” è solitamente eseguita sugli anelli

di controllo: in questo caso i vantaggi ottenibili in termini di au-

mento delle prestazioni superano di gran lunga gli svantaggi

legati alla necessità di ricorrere a circuiti logici aggiuntivi, con

conseguente aumento degli ingombri.

Soddisfare le esigenze dei progetti ad alte prestazioni della

prossima generazione è un compito oneroso utilizzando le

architetture FPGA tradizionali. Grazie all’approccio “regis-

ters-everywhere”, la nuova architettura di Altera garantisce le

prestazioni richieste da tutte quelle applicazioni che necessi-

tano di ampiezze di banda sempre più estese.

Fig. 5 – Esempio di operazione di Hyper-Pipelining effettuata nell’architettura

HyperFlex

Fig. 4 – Esempio di pipelining eseguito nelle architetture di tipo tradizionale