DIGITAL

FPGA

40

- ELETTRONICA OGGI 451 - GENNAIO/FEBBRAIO 2016

Aumentare le prestazioni

con un’architettura FPGA

di concezione innovativa

A

l fine di rispondere in maniera adeguata

alla richiesta di dispositivi caratterizzati

da prestazioni sempre più spinte, i pro-

getti dei circuiti integrati devono “anticipare i

tempi “ per poter garantire la disponibilità di

prodotti in linea con le aspettative del mercato.

Questo aspetto, ampiamente sperimentato in

tutti i settore della progettazione dei semicon-

duttori, assume una particolare rilevanza in

particolari segmenti, come ad esempio quello

dell’elaborazione ad alte prestazioni (HPC - High

Performace Computing), dove la richiesta di

throughput e di ampiezza di banda sempre

maggiori aumenta a un ritmo esponenziale. In

questo settore molti progetti hanno adottato

FPGA al fine di soddisfare questa “fame” di pre-

stazioni ma, anche utilizzando le architetture più

avanzate, i progettisti hanno dovuto ricorrere a

bus on chip molto ampi – spesso fino a 2.048

bit – per l’implementazione dei loro

design.Learchitetture

di routing (che definiscono i collegamenti tra i blocchi logici

e quelli di I/O e tra i vari blocchi logici) possono consentire

una disposizione più efficiente dei fili (wire) grazie all’ado-

zione di tecniche di ottimizzazione e di strutture di routing

di tipo gerarchico. In ogni caso, il raddoppio del numero dei

conduttori si traduce in un incremento dell’area del chip e

della dissipazione di potenza. La metodologia tradizionale

che prevede la realizzazione di coppie di registri per la LUT

(Look-Up-Table) adottata per tutte le architetture del nucleo

(core) delle attuali FPGA penalizza la logica per consentire

l’aggiunta dei registri di pipeline. L’operazione di pipelining

eseguita nelle architetture di tipo tradizionale comporta anche

un aumento del ritardo in quanto un segnale deve essere

instradato verso l’ingresso e l’uscita di un blocco logico. Ciò

contribuisce a diminuire l’efficacia delle tecniche di pipelining,

in special modo nel caso in cui i ritardi imputabili al routing

rappresentano il maggior contributo al ritardo totale.

Un altro problema è la minimizzazione delle variazioni del

clock e dello skew (disallineamento), la cui importanza au-

menta al crescere della velocità. Per frequenze superiori a

500 MHz, è necessario utilizzare nuove soluzioni di clocking in

quanto la semplice aggiunta di alberi per la distribuzione del

clock (clock tree) non risulta più sufficiente.

Un’architettura innovativa

Di recente Altera ha introdotto una nuova architettura per i pro-

pri FPGA denominata HyperFlex che sfrutta un certo numero

di innovazioni per garantire il raddoppio delle prestazioni. Per

conseguire questi miglioramenti in termini di prestazioni gli

Mike Hutton

Architect, IC Design and Engineering

AlteraCon la nuova architettura HyperFlex sviluppata

da Altera è possibile soddisfare le esigenze

di mercati come quelli dell’High Performance

Computing che richiede throughput e ampiezza

di banda sempre maggiori

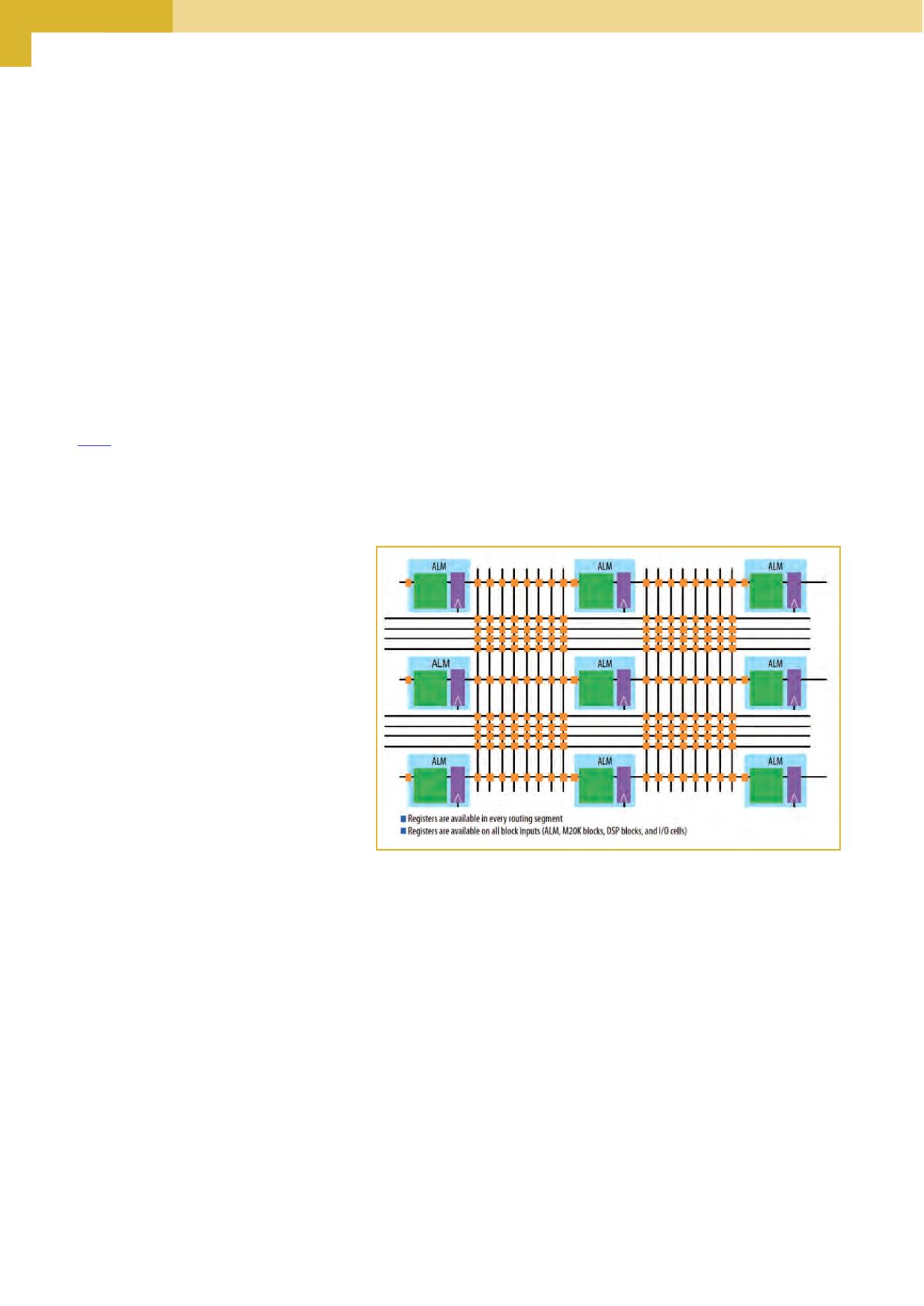

Fig. 1 – L’approccio “Registers Everywhere” utilizzato per la realizzazione dell’architettura

HyperFlex