27

RADAR |

IN TEMPO REALE

EMBEDDED

60 • MAGGIO • 2016

numerico DSP, che ne consen-

tono l’utilizzo nei sistemi di

rilevamento radar ma anche

nella gestione delle Software

Defined Radio di prossima ge-

nerazione. Le nuove FlexorSet

Model 7070-317 con interfaccia

PCIe e FlexorSet Model 5973-

317 in formato 3U VPX incor-

porano entrambe lo stadio di

conversione Flexor Model 3316

A/D dotato di otto canali DDC

(Digital Down Converter) con

risoluzione di 16 bit e banda di

250 MHz. Inoltre, ciascuno de-

gli otto canali ha una propria

configurazione del filtro di de-

cimazione per le trasformate di

Fourier FFT che può essere ca-

librato dal valore minimo di 2

fino al massimo di 65536 nella

fase di programmazione, nella

quale si può anche sintonizzare

finemente la frequenza centra-

le delle trasformate con risoluzione di 32 bit dal-

la continua fino alla massima frequenza di 250

MHz. In entrambe, la dotazione di memoria con-

siste in 4 GByte di Sdram DDR3 e per entrambe

viene fornito il supporto del Configuration Ma-

nager GateXpress Fpga-PCIe che consente di

riconfigurare dinamicamente l’Fpga attraverso

l’interfaccia PCIe. Infine, ci sono due versioni con

tolleranza termica adatta alle applicazioni indu-

striali oppure estesa per la configurazione rug-

ged idonea all’impiego militare.

Radar matematici

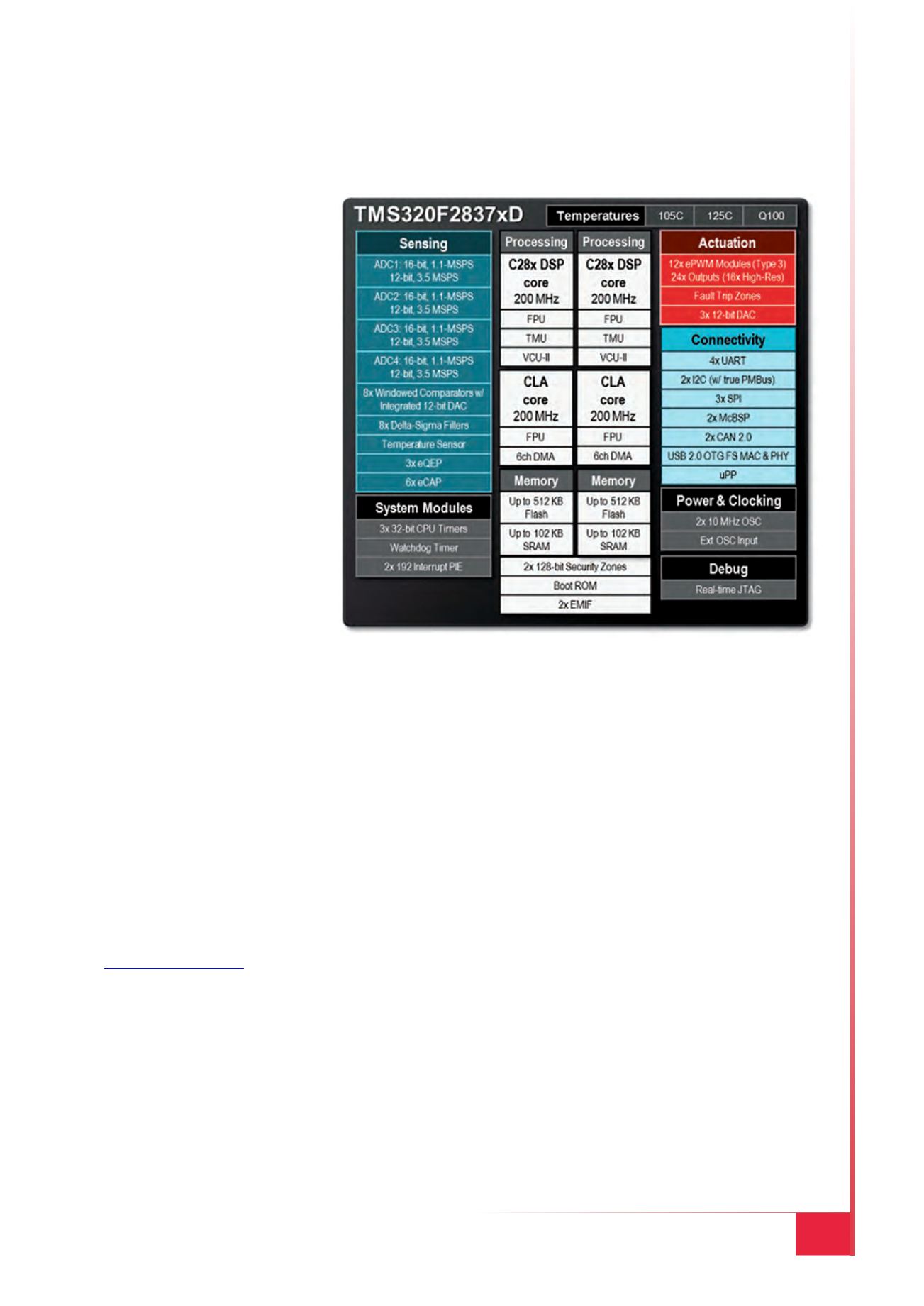

Texas Instrumentspropone il microcontrollore

TMS320F28377D della famiglia C2000 Delfino,

con una dotazione fatta apposta per la rilevazio-

ne radar. Il sofisticato stadio PWM a 24 canali ha

un preciso controllo del duty cycle e può genera-

re dodici impulsi radar che vengono poi rilevati

attraverso quattro canali di ricezione dotati di

altrettanti convertitori A/D ciascuno dei quali ha

una risoluzione di 16 bit, un tempo di conversio-

ne di 910 ns e una velocità di campionamento di

1,1 milioni di campioni al secondo, per un tota-

le di 4,4 MSPS. In alternativa, si possono anche

utilizzare i convertitori ADC in dotazione con

risoluzione di 12 bit che hanno un tempo di con-

versione ancor migliore di 286 ns e in questo caso

si può ottenere una velocità di campionamento

massima di 3,5 MSPS su ciascun ADC e di 14

MSPS in totale.

Il potente motore matematico è composto da

due core TMS320C28x DSP con clock di 200

MHz che integrano sia una Trigonometric Math

Unit (TMU) sia una Viterbi Complex Math Unit

(VCU-II) e sono affiancati da altrettanti due ac-

celeratori CLA con medesimo clock di 200 MHz

in grado di eseguire 800 MIPS (milioni di istru-

zioni al secondo) a virgola mobile in singola pre-

cisione e 200 MMACS (milioni di moltiplicazioni

con accumulo al secondo). Il microcontrollore vie-

ne fornito in quattro configurazioni con 1 MByte

o 512 Kbyte di memoria Flash, 9 o 12 canali

ADC da 16 bit, 20 o 24 ADC da 12 bit e 97 o 169

GPIO, il tutto in package 176Hlqfp o 337nFbga

con tolleranza termica standard da -40 a +105

°C oppure estesa da -40 a +125 °C. In dotazione

c’è anche il Delfino Experimenter Kit, che aiuta

il progettista a realizzare sistemi radar orientati

alle applicazioni.

Fig. 5 – I microcontrollori Texas Instruments F2837xD della fami-

glia Delfino C2000 hanno una dotazione specifica per trasmette-