VIII

Power

POWER 13 -

APRILE 2017

Gli FPGA si stanno rapidamente affer-

mando come gli elementi chiave in un

gran numero di progetti embedded

grazie alla loro struttura che può esse-

re riconfigurata in modo dinamico e

alla capacità di eseguire elaborazioni in

parallelo. Tali caratteristiche rendono que-

sti dispositivi programmabili ideali per l’uso in sistemi

destinati ad applicazioni quali reti neurali convoluziona-

li (CNN) e apprendimento automatico (machine lear-

ning), apparecchiature di comunicazione broadcast e si-

stemi avanzati di assistenza alla guida (ADAS – Advanced

Driver Assistance System). Adatti per l’interfacciamento

con una pluralità di altri componenti e sotto-sistemi e

in grado di supportare dispositivi quali

transceiver, PLL e memorie, gli FPGA

richiedono parecchie tensioni di alimen-

tazione diverse, ciascuna delle quali dif-

ferisce in termini di valori di tensione,

corrente e risposta ai transitori. Il core

dell’FPGA, richiede correnti dell’ordine

delle decine di A. Alcuni progetti pre-

vedono correnti fino a 90A, a fronte di

tensioni di valore ridotto, pari a esempio

a 0,95 VDC, mentre memorie, interfac-

ce e component logici legacy operano

con tensioni i cui valori sono compresi

tra 1,5 e 3,3 VDC. Nella progettazione

dell’alimentatore è necessario tenere

presenti altri fattori come l’immunità al

rumore. Componenti come i transceiver,

e i PLL in particolare, richiedono power

rail (ovvero terminali che forniscono l’a-

limentazione) molto “puliti” al fine di

impedire l’ingresso del jitter nel sistema.

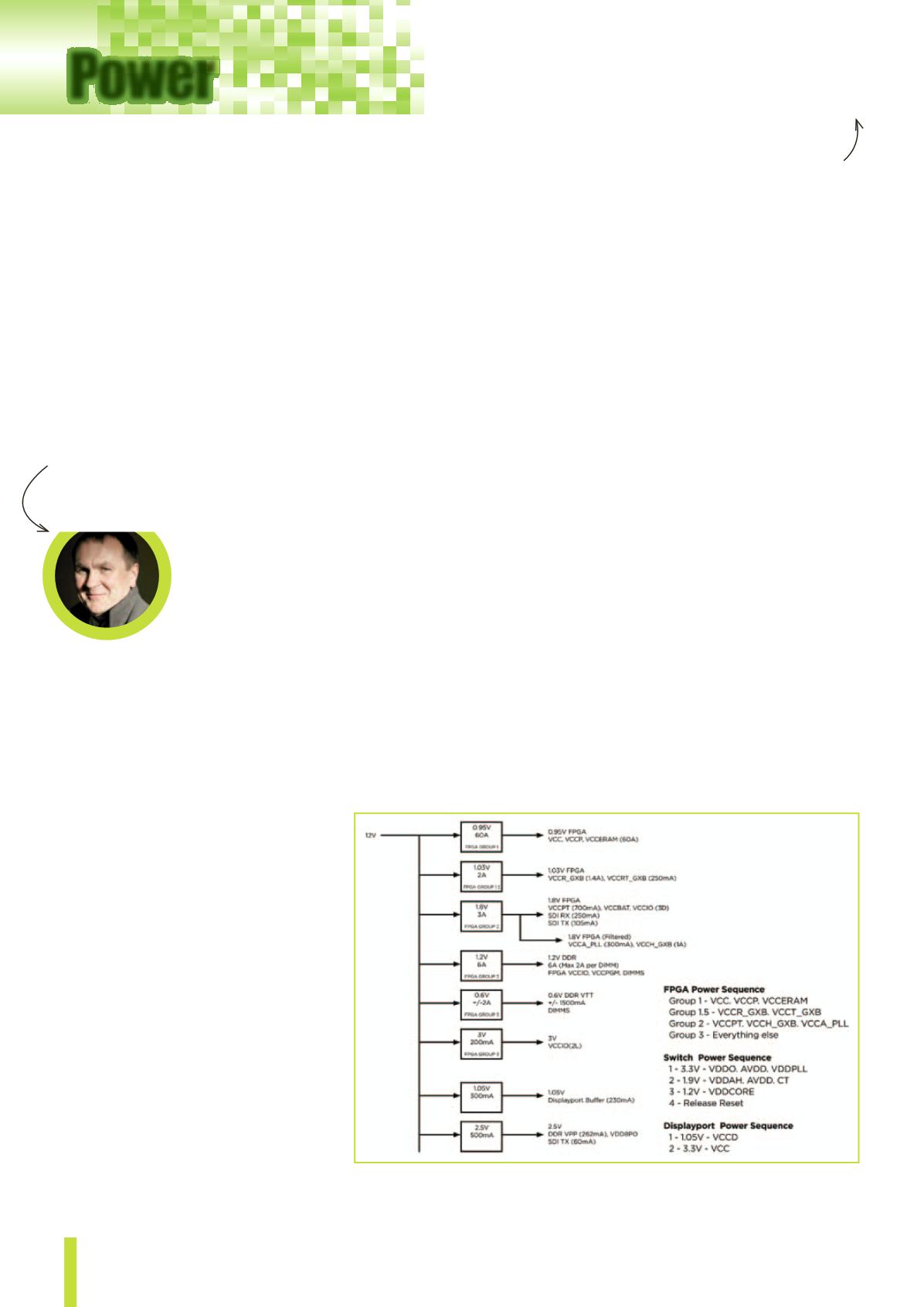

Nel momento in cui devono affrontare il problema dell’a-

limentazione di un nuovo progetto basato su FPGA o SoC,

i progettisti dovrebbero compilare un elenco che contie-

ne tutti i terminali (rail) di tensione richiesti, unitamente

ad altri parametri critici come ad esempio la corrente di

picco. Nel caso di progetti complessi, un altro aspetto da

tenere in considerazione è la necessità di raggruppare o

definire la sequenza con la quale avvengono le operazioni

di accensione (power up) e spegnimento (power down)

dei singoli terminali di alimentazione. Questo elenco “ad

albero”, riportato in figura 1, riporta tutti i requisiti in

termini di potenza. È necessario prestare attenzione non

solo alle varie tensioni di ingresso, ma anche all’alimenta-

zione in ingresso. Con tutti questi elementi a disposizione

John Dillon •

Intel

Un’utile guida alla progettazione

dell’alimentazione di sistemi basati

su FPGA o SoC

Gli FPGA e i SoC di ultima generazione possono richiedere una corrente fino a 90A

e la presenza di più terminali di alimentazione che necessitano di una particolare

attenzione nelle fasi di power up/power down

Fig. 1

– Esempio di un EPE (Early Power Estimator) per un progetto basato su FPGA

(Fonte: Enpirion)