X

Power

POWER 13 -

APRILE 2017

La messa in sequenza

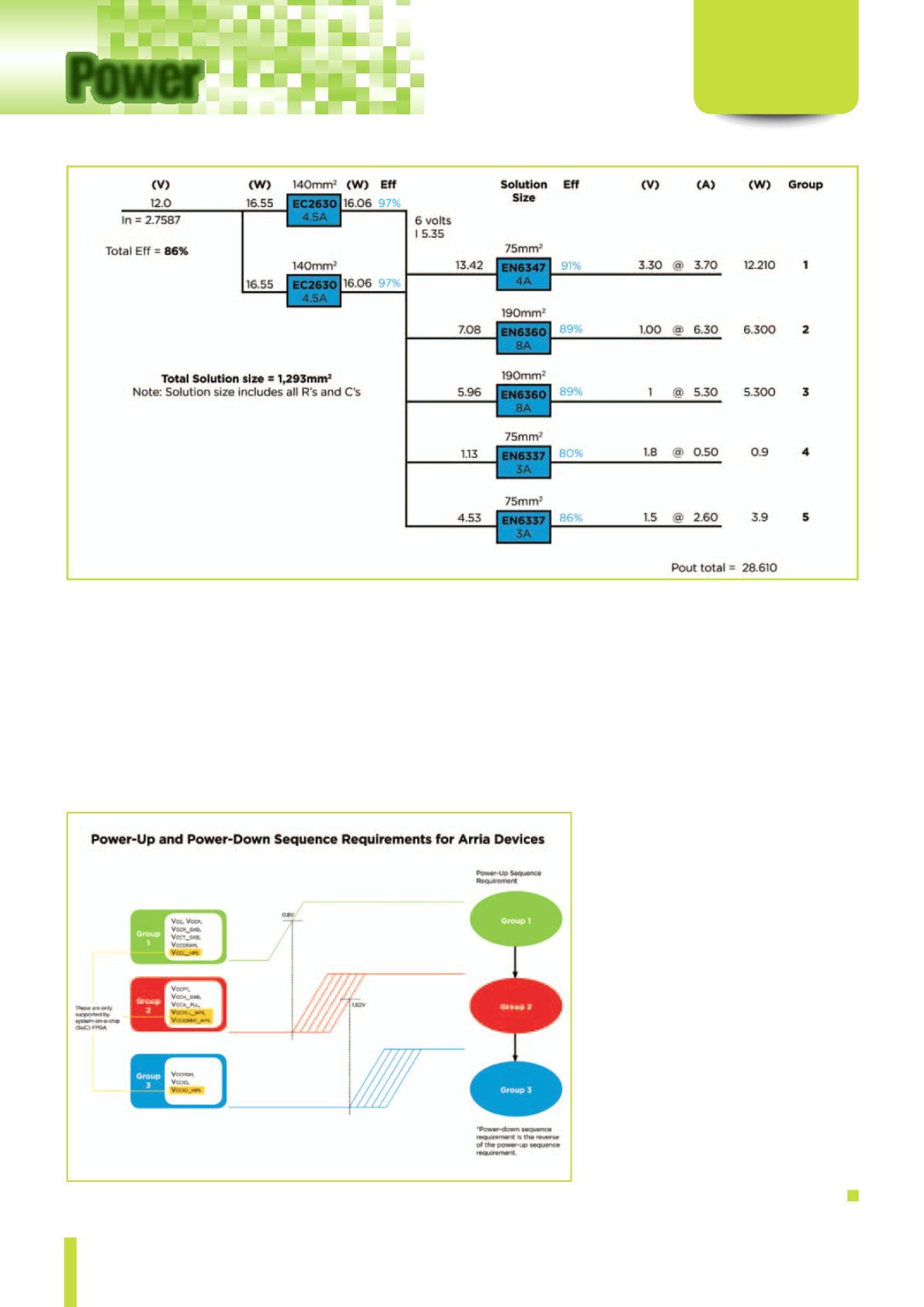

Arrivati a questo punto del progetto dello schema di ali-

mentazione, è necessario prestare attenzione ai requisiti

relativi allamessa in sequenza. Comemenzionato in prece-

denza, le linee guida relative all’utilizzo degli FPGA sotto-

lineano le specifiche relative a ciascuna sequenza di power

up/power down che devono essere rispettate. L’esempio

riportato in figura 5 evidenzia che tre differenti gruppi

di potenza devono essere posti in sequenza: nella figura

sono anche indicati i valori di tensione in corrispondenza

dei quali i gruppi successivi possono iniziare il power

up.Ilprocesso di power-down è esattamente l’inverso di quello

di power up. In questo caso il progettista deve considerare

il tempo richiesto per la scarica dei condensatori presenti

nel “power tree”. Per poter eseguire questa operazione è

necessario ricorrere a MOSFET in grado di supportare i

banchi di condensatori di maggiori dimensioni presenti

nello schema di alimentazione. Ovviamente, è importan-

te che i MOSFET utilizzati per la carica siano in grado

di gestire i transitori di potenza e funzionare nel rispetto

dei parametri di sicurezza in modo da

non causare eccessive sollecitazioni di

natura termica. Per gestire la sequenza di

power-up/power-down si potrebbe ricor-

rere all’uso di FPGA come ad esempio i

dispositivi della famiglia MAX10 di Intel

PSG. Nella figura 6 è riportato un sem-

plice schema del circuito richiesto per

espletare tale compito con un gruppo di

quattro terminali di alimentazione. È uti-

le osservare che potrebbe essere richie-

sto un alimentatore ausiliario per poter

innescare il processo di messa in sequen-

za del circuito di shutdown di MAX10

per un periodo di almeno 100 ms dopo

l’inizio dell’attivazione del processo di

power down. Seguendo le indicazioni

fornite in questo articolo un progettista

sarà in grado di sviluppare uno schema

di alimentazione da utilizzare in progetti

complessi basati su FPGA.

FPGA

Fig. 5

– Sequenze di power-up e power-down

Fig. 4

– Esempio di schema di un “albero della potenza”