Progettazione di circuiti sequenziali low power con clock gating

In questo articolo si analizza un modo efficace per progettare circuiti sequenziali low power, con la tecnica clock gating e con l’ausilio di un contatore Johnson programmabile multi-stage, che garantisce un basso consumo di potenza dinamica rispetto ai circuiti convenzionali

Con le tecnologie attuali, le frequenze di clock sempre più vantaggiose e la crescente enfasi sulla riduzione della potenza, il design a basso consumo sta assumendo un ruolo fondamentale. I team di progettazione non possono più preoccuparsi solo dell’isolamento e delle relative tecniche sul PCB. Con la maggior parte dei SoC contenenti più circuiti sequenziali, ogni bit è importante, rendendo così ancora più incisiva la progettazione di modelli efficienti a bassa potenza. I circuiti sequenziali sono prevalentemente utilizzati per progettare macchine a stati finiti (FSM), divisori di clock e contatori.

In un tipico design, tutte le operazioni del computer (aritmetiche, logiche e processi di memoria) vengono eseguite in modo sincrono rispetto al clock, aumentando quindi il numero di circuiti sequenziali in un sistema elettronico. A causa della concorrenza messa in atto per salvare ogni mW, in questa epoca di dispositivi a batterie mobili è importante non solo separare il circuito in domini e sottodomini in termini di PCB, ma anche e soprattutto abilitare e disabilitare i sottosistemi a livello software.

Il contatore Johnson fornisce particolari tipi di sequenze di dati in modo sincrono, essenziali in diverse importanti applicazioni (ad esempio, convertitore D/A, FSM e divisori di clock). Con una maggiore integrazione di dispositivi, i blocchi in un SoC sono formati da più sottosistemi in esecuzione a diverse frequenze, che vanno dai MHz ai GHz.

In questo articolo sarà descritto un metodo di risparmio energetico ottenuto sostituendo più divisori di clock con un sistema programmabile (Johnson Counter) multi-stage con clock gating, che può fornire fattori di divisione di clock che vanno da 8 a qualsiasi valore.

Contatore Johnson (Johnson ring counter)

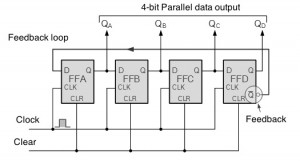

Il contatore Johnson è un insieme di registri a scorrimento disposti in cascata, con uscita invertita dell’ultimo flip-flop D e reintrodotto come ingresso al primo flip-flop; tutti gli altri flip-flop sono collegati all’uscita del precedente (Fig, 1).

Il vantaggio principale di questo tipo di contatore è che si ha bisogno solo della metà del numero di flip-flop rispetto a un ring counter standard; un contatore Johnson di “n-stage” farà circolare un singolo bit di dati dando una sequenza di 2n stati diversi.

Invece, un ring counter standard è formato da una sequenza di registri a scorrimento con uscita non invertita in feedback. Tipicamente, un modello composto di un singolo bit 1 viene fatto circolare e lo stato si ripete ogni N cicli di clock se vengono utilizzati N flip-flop. Può essere usato come un contatore di ciclo a N stati.

Nel modello Johnson, l’inversione di Q, prima di essere reimmessa nell’ingresso D, seleziona il sistema stesso a contare in modo differente. Invece di contare attraverso una serie fissa di modelli come il contatore ring standard, ad esempio per un contatore a 4 bit, “0001” (1), “0010” (2), “0100” (4), “1000” (8) e ripetere, il contatore Johnson 4 bit passa blocchi di quattro logico “0” e poi quattro logico “1” producendo così un pattern a 8 bit. Poiché l’uscita invertita Q è collegata all’ingresso D, questo modello 8-bit si ripete continuamente. Ad esempio, “1000”, “1100”, “1110”, “1111”, “0111”, “0011”, “0001”, “0000”. Tipica applicazione dei contatori Johnson è la conversione digitale-analogico, così come modelli di riconoscimento dei bit. In particolare, un contatore Johnson a 3 stadi può essere utilizzato come generatore di 3 onde quadre sfasate di 120°, collegando le uscite in A, B e not-B della figura 1.

Collegando semplici porte logiche come AND o OR alle uscite del flip-flop del circuito, può essere utilizzato per rilevare un numero o valore impostato. Contatori a 2, 3 o 4 stadi possono anche essere utilizzati per dividere la frequenza del segnale di clock, variando le loro connessioni di feedback. Un esempio di contatore commerciale è CD4017 di Texas Instruments, utilizzato nei circuiti elettronici come divisore sincrono.

Problematiche nei circuiti sequenziali

Il più grande svantaggio del circuito mostrato in figura 1 è la non configurabilità per la modifica del fattore di divisione. Un design di N-flip-flop può produrre solo un clock di 2N come periodo.

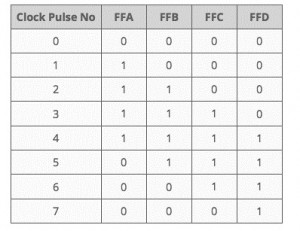

Inoltre, il design non è a basso consumo e non fornisce un meccanismo per risparmiare potenza dinamica efficiente. Ad esempio, si può vedere nella figura 2 che Q3 cambia la sua uscita solo in impulsi di clock 1 e di impulsi di clock 5. Per tutti altri stati di clock il flip-flop memorizza più e più volte gli stessi dati e questo porta all’inutile dissipazione di potenza nei cicli di clock.

Clock Gating

Clock gating è una tecnica che può essere utilizzata per controllare la potenza dissipata a causa dei segnali di clock. Nei circuiti digitali sincroni, il clock è responsabile di una parte rilevante della dissipazione di potenza (fino al 40%). La tecnica Clock Gating sequenziale ha dimostrato di ridurre la potenza fino al 60% su blocchi di progettazione.

I circuiti sequenziali in un sistema sono considerati la principale fonte di potenza dissipata, in particolare dal clock, che è l’unico segnale che passa per tutto il tempo.

Ogni sistema digitale esegue le proprie operazioni funzionali alla cadenza di uno o più segnali di clock che rappresentano a sua volta un indice di elaborazione del processore. La tecnica Clock Gating consiste nello spegnere i sottosistemi del processore che non lavorano, oppure ridurre la frequenza del clock al valore minimo. Questo si ottiene attivando il clock solo per i blocchi che ne necessitano.

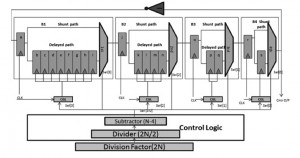

Ogni circuito sequenziale può essere migliorato mediante un’efficace tecnica del clock gating. Il contatore Johnson mostrato in figura 1 è ri-progettato (Fig. 3) per sostenere fattori di divisione flessibili, al fine di produrre frequenze di uscita variabili.

Per far ciò, vengono aggiunti più stadi di ritardo, con la combinazione logica necessaria per scegliere il fattore di divisione desiderato.

La figura 3 rappresenta il circuito Johnson migliorato: comprende le fasi di ritardo in cascata B1, B2, B3, B4, un inverter I, un ingresso di clock CLK di riferimento, una logica clock gating (CGL) e una di controllo (Divisore e Subtractor) per selezionare la combinazione di flip-flop desiderata.

Nel circuito si sono impiegati 19 flip-flop D che possono raggiungere qualsiasi fattore di divisione compreso tra 8 e 38. I fattori di divisione richiesti possono essere ulteriormente aumentati, con l’aggiunta di flip-flop e multiplexer.

Come visualizzato in figura 3, al fine di risparmiare energia, l’uscita del circuito di controllo viene alimentata da CGL per abilitare o disabilitare il clock di ritardo in conformità con il fattore di divisione richiesto. Dato un fattore di divisione di 2N, N è il numero di flip flop richiesti per raggiungere la frequenza di clock voluta.

Un sottrattore è stato inserito per facilitare la selezione del multiplexer e abilitare la logica clock gating.

In base al fattore di divisione fornito dall’utente, il sottrattore fornisce N-4 come uscita e ciascuno dei bit dell’uscita binaria del sottrattore funziona come le corrispondenti linee di selezione per i 4 multiplexer (1°, 2°, 3°, 4°) e consente a CGL di cancellare il clock dei flip-flop inutilizzati.

Questo rende il design programmabile, riducendo il consumo di potenza dinamico del contatore.

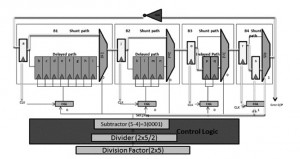

Si consideri come esempio un fattore di divisione 10, cioè 2N = 10 (Fig. 4). Poiché un tipico contatore Johnson richiede N flip-flop per un fattore di divisione di 2N, per ottenere un fattore di divisione 10 sono necessari 5 flip-flop. Il subtractor alimenterà le linee di selezione del multiplexer, con rappresentazione binaria 0001; questa controlla non solo la logica clock gating ma seleziona anche il percorso tra shunt e quelli ritardati.

Con il clock gating aggiunto nella progettazione, qualsiasi logica sequenziale formata da registri a scorrimento può essere resa più efficiente. Una raccolta di tali circuiti SoC è in grado di risparmiare energia e aumentare la durata della batteria del dispositivo.

Maurizio Di Paolo Emilio

Contenuti correlati

-

USB Power Delivery: efficienza e convenienza per l’infotainment a bordo veicolo

I controllori USB PD di TI sono una soluzione su chip singolo che permette di migliorare l’efficienza e la densità di potenza dei prodotti USB destinati al mondo automotive Leggi l’articolo completo su EO Power 36

-

Il nuovo centro di distribuzione dei prodotti di TI

Texas Instruments (TI) ha aperto un nuovo centro per la distribuzione dei prodotti a Dreieich, nei pressi di Francoforte. Il nuovo impianto, che ha un’estensione di 9.000 metri quadrati, dispone di nuove funzionalità di automazione. Può infatti...

-

Progettazione di un circuito di precarica attiva con condensatore DC-Link ad alta tensione

Questo articolo presenta il processo di progettazione necessario per calcolare gli adeguati valori dei componenti che contribuiscono a ottenere il profilo di carica desiderato Leggi l’articolo completo su EO 521

-

I miglioramenti nella tecnologia RFID danno origine a nuove applicazioni

L’identificazione a radiofrequenza (RFID) è una tecnologia consolidata che viene impiegata da molti anni, con l’introduzione dei primi esempi di transponder RF passivi che risale agli anni 70. Probabilmente la usate tutti i giorni senza accorgervene, ma...

-

Come migliorare la sicurezza negli inverter di trazione dei veicoli elettrici

I progettisti di veicoli elettrici possono aumentare la sicurezza e l’affidabilità dei sistemi a inverter di trazione monitorando la soglia di tensione del gate Leggi l’articolo completo su EO520

-

Finanziamenti per 1,6 miliardi per Texas Instruments

Texas Instruments (TI) ha firmato un memorandum d’intesa preliminare non vincolante con il Dipartimento del Commercio degli Stati Uniti per un finanziamento diretto fino a 1,6 miliardi di dollari. Questa operazione rientra nell’ambito del CHIPS and Science...

-

Un processore con LPDDR4 integrata accelera lo sviluppo di applicazioni

Il System-in-Package rappresenta una valida scelta di progettazione e può essere determinante per lo sviluppo di svariate applicazioni e dispositivi di tipo general purpose, nonché per soluzioni compatte e ad alte prestazioni Leggi l’articolo completo su EO519

-

Progettazione di un’applicazione per supportare ampi intervalli di tensione di ingresso e della batteria

Oltre a contribuire a ridurre i tempi di progetto, l’utilizzo di un caricabatterie ad ampio VIN e ampia VOUT permette di valutare nuove tecnologie, come la ricarica bidirezionale a energia solare Leggi l’articolo completo su EO519

-

Texas Instruments e Delta Electronics insieme per le soluzioni per EV

Texas Instruments (TI) ha stretto una collaborazione a lungo termine con Delta Electronics per creare soluzioni di ricarica di bordo e alimentazione di nuova generazione per veicoli elettrici (EV). Questa collaborazione sfrutterà le capacità di ricerca e...

-

Realizzare telecamere smart basate sull’AI con un processore “ad hoc”

Il processore AM62A è progettato per applicazioni di visione da bassa a media che richiedono una o due telecamere. Grazie al suo innovativo acceleratore per AI, all’encoder/decoder H264/H265 e al processore ISP (Image Sensor Processor) integrato dotato...