Come ottenere la massima efficienza nella conversione AC-DC con i controllori per PFC totem pole “bridgeless”

L’energia elettrica viene fornita dalla rete sotto forma di corrente alternata (AC) ma, poiché un gran numero di dispositivi di uso quotidiano richiede una potenza in corrente continua (DC power), gli alimentatori AC/DC preposti a effettuare questa conversione sono tra i carichi più comuni della rete elettrica. La sempre maggiore focalizzazione sull’efficienza energetica, necessaria per la salvaguardia dell’ambiente e una gestione ottimale dei costi operativi, ha accentuato l’importanza dell’efficienza del funzionamento di questi alimentatori.

L’efficienza, intesa come misura del rapporto tra la potenza in ingresso e la potenza fornita al carico, è un concetto ben noto. In ogni caso, il fattore di potenza in ingresso ha anch’esso un impatto significativo. Il fattore di potenza (PF – Power Factor) descrive il rapporto tra la potenza utile (reale) e la potenza totale (apparente, espressa in kVA) consumata da qualsiasi dispositivo alimentato in AC, alimentatori compresi. Il fattore di potenza fornisce un’indicazione dell’efficienza con la quale la potenza elettrica consumata è convertita in lavoro utile in uscita.

Se il carico è puramente resistivo, il fattore di potenza assumerà un valore pari a uno, ma ogni elemento reattivo presente all’interno del carico contribuirà a ridurre il fattore di potenza, ragion per cui il valore della potenza apparente sarà superiore a quello della potenza reale, con conseguente diminuzione dell’efficienza.

Un fattore di potenza inferiore all’unità è causato dallo sfasamento tra tensione e corrente, una situazione comune nel caso di carichi induttivi. Esso può anche essere imputabile a un elevato contenuto armonico oppure a una forma d’onda di corrente distorta, uno scenario tipico in presenza di alimentatori a commutazione (SMPS – Switched Mode Power Supply) o di altre tipologie di carichi elettronici discontinui.

Correzione del fattore di potenza

Poichè numerosi SMPS che non prevedono la correzione del fattore di potenza assorbono correnti di valore più elevato rispetto ad analoghi alimentatori dotati di correzione di questo fattore, per potenze superiori a 70 W, le normative in vigore richiedono ai progettisti di integrare circuiti di correzione in grado di riportare il fattore di potenza a un valore prossimo all’unità. La tecnica più comunemente utilizzata per la correzione del fattore di potenza (PFC – Power Factor Correction) attiva prevede il ricorso a un convertitore boost per convertire la tensione rettificata della linea in una tensione DC di valore più elevato e quindi ricorrere alla modulazione PWM (Pulse Width Modulation) per regolare il livello della tensione DC.

Benché si tratti di una tecnica che fornisce buoni risultati ed è semplice da implementare, non è esente da problematiche. I moderni standard che disciplinano l’efficienza energetica, come lo standard 80+ Titanium, richiedono elevati valori di efficienza per un’ampia gamma di potenze ed efficienza di picco fino al 96% (al 50% del carico). Poiché le perdite del convertitore DC/DC che segue lo stadio PFC possono essere stimate pari al 2%, le perdite imputabili alla rettificazione di linea e allo stadio PFC dovrebbero ammontare anch’esse al 2%, un obiettivo difficile da raggiungere per la presenza di diodi nel rettificatore a ponte.

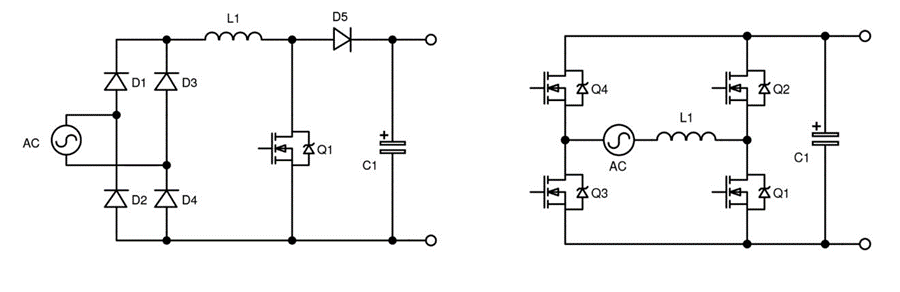

Fig. 1 – Schemi di circuiti PFC di tipo totem pole tradizionale (a sinistra) e “senza ponte” (destra)

La sostituzione del diodo boost (D5 dello schema di figura 1) con un rettificatore sincrono permette di aumentare l’efficienza. Oltre a ciò, poiché sono richiesti solamente due diodi rettificatori di linea, che possono essere anche rettificatori sincroni (Q3, Q4 di figura 1), l’efficienza è può essere ulteriormente incrementata. Questa tecnica è conosciuta come TPPFC (Totem Pole PFC) e nel caso si utilizzassero un induttore ideale e commutatori “perfetti” (ovvero privi di perdite), consentirebbe di ottenere livelli di efficienza molto prossimi al 100%. Anche se i moderni MOSFET assicurano eccellenti prestazioni, non si possono comunque considerare commutatori “perfetti” anche quando sono impiegati in parallelo. Di conseguenza è opportuno prendere in considerazione l’ipotesi di ricorrere a semiconduttori WBG (Wide BandGap) per l’implementazione della topologia PFC totem pole.

Affrontare in modo efficace il problema delle perdite

Poichè le frequenze di commutazione tendono ad assumere valori sempre più elevati, l’impatto delle perdite dinamiche nei dispositivi di commutazione è destinato ad aumentare. Tali perdite sono ascrivibili al recupero inverso del MOSFET configurato come commutatore del ramo (leg) veloce del totem pole, quando il suo diodo intrinseco (body diode) conduce durante il tempo morto (dead time) di commutazione e la carica immagazzinata associata deve essere rimossa, oltre che dalla carica/scarica della capacità di uscita del commutatore.

Poiché le perdite dinamiche possono essere significative per i MOSFET in silicio, sempre più spesso i progettisti contemplano l’uso di materiali semiconduttori ad ampia banda proibita come il carburo di silicio (SiC) e il nitruro di gallio (GaN) nelle applicazioni TPPFC. I dispositivi realizzati con questi materiali hanno l’ulteriore vantaggio di poter funzionare a frequenze più elevate e operare ad alte temperature, due caratteristiche senza dubbio apprezzate nelle applicazioni di potenza.

La conduzione critica (CrM – Critical Conduction Mode) è la modalità di conduzione preferita per circuiti TPPFC specialmente nel caso in cui le potenze in gioco sono dell’ordine di alcune centinaia di Watt in quanto garantisce un buon compromesso tra efficienza e prestazioni in termini di emissioni EMI. La modalità di conduzione continua (CCM – Continuous Conduction Mode) permette di ridurre ulteriormente il valore RMS della corrente nei commutatori e le perdite per conduzione, consentendo l’uso della topologia TPPFC in applicazioni con potenze dell’ordine dei kilo-Watt.

Anche utilizzando la modalità CrM la diminuzione dell’efficienza può essere significativa (fino al 10%) in presenza di carichi di valori ridotti. Ciò rappresenta un serio problema nel momento in cui viene richiesto il rispetto dei limiti imposti per i consumi di energia in stand-by o in assenza di carico (no-load). Per ovviare a tale problema si potrebbe agganciare (o limitare – fold-back) la massima frequenza consentita, forzando il circuito a operare in modalità DCM (Discontinuous Conduction Mode) con carichi ridotti, dove le correnti di picco più elevate sono comunque inferiori rispetto a quelle di un’implementazione CrM equivalente.

Una configurazione TPPFC con funzionamento in modalità CrM e aggancio di frequenza rappresenta una buona soluzione per carichi di valori medi che assicura ottimi livello di efficienza sull’intero intervallo di carico, specialmente nel caso in cui si utilizzino commutatori WBG per il ramo ad alta frequenza.

Ulteriori problematiche

Una volta risolto il problema dell’efficienza, rimane un ultimo ostacolo da superare. La configurazione adottata prevede la presenza di quattro dispositivi attivi che devono essere pilotati in modo sincrono e il rilevamento della corrente nulla (zero current crossing) nell’induttore per forzare la modalità CrM. Il circuito deve essere in grado di entrare e uscire automaticamente dalla modalità DCM in funzione del carico e ciò deve essere fatto garantendo il mantenimento di un valore elevato del fattore di potenza e la possibilità di generare un segnale PWM per regolare l’uscita. Senza dimenticare la necessità di prevedere circuiti di protezione, come a esempio quelli contro le sovracorrenti e le sovratensioni.

In considerazione del livello di complessità, il miglior approccio consiste nell’implementazione degli algoritmi di controllo in un microcontrollore. Una soluzione di questo tipo potrebbe risultare costosa, oltre a richiedere la generazione e il debug di codice, un compito che molti progettisti preferirebbero evitare.

Una soluzione “code-free” per circuiti TPPFC operanti in modalità CrM

Le soluzioni di controllo di circuiti TPPFC integrate assicurano numerosi vantaggi tra cui elevate prestazione, riduzione dei tempi di sviluppo e bassi rischi di progetto, oltre a eliminare il ricorso a un microcontrollore e la relativa scrittura di codice. Una soluzione integrata di questo tipo è il controllore per TPPFC a segnali misti NCP1680 di onsemi che opera in modalità CrM con controllo CoT (Constant on Time) per assicurare elevati livelli di efficienza sull’intervallo di carico. Questo dispositivo effettua la commutazione quasi risonante (valley switching) durante il foldback (limitazione) della frequenza per carichi di valore ridotto in modo da migliorare l’efficienza commutando in corrispondenza del valore minimo di tensione. L’anello di controllo della tensione digitale è compensato internamente per ottimizzare le prestazioni su tutto il range di carico, preservando nel contempo la semplicità del processo di design (Fig. 2).

Fig. 2 – Il controllore NCP1680 di onsemi è una soluzione semplice ed elegante per circuiti TPPFC che non richiede la scrittura di codice

Alloggiato in un package SOIC-16 di piccole dimensioni, questo innovativo controllore sfrutta un approccio proprietario caratterizzato da perdite ridotte per il rilevamento della corrente, mentre la limitazione della corrente su base ciclica assicura un elevato grado di protezione senza necessità di ricorrere a un sensore a effetto Hall esterno, il che si traduce in una riduzione di complessità, dimensioni e costi.

Tutti gli algoritmi di controllo necessari sono inclusi all’interno del circuito integrato, mettendo così a disposizione dei progettisti una soluzione collaudata che permette di ridurre i rischi di design e garantisce elevate prestazioni a un costo decisamente competitivo.

Yong Ang Strategic Marketing Director (onsemi)

Contenuti correlati

-

I sensori induttivi contribuiscono all’evoluzione dell’automazione industriale

Robot e cobot (robot collaborativi) sono in grado di svolgere un maggior numero di attività in fabbrica, gestire compiti (task) più complessi e operare a una velocità più elevata rispetto al passato Leggi l’articolo completo su Embedded...

-

Un’analisi dell’impatto della decisione dell’NHTSA relativa all’AEB sui consumatori e sull’industria automotive

Per comprendere se lo standard di NHTSA relativo all’AEB (AEB – Automatic Emergency Braking) sarà recepito in tempi sufficientemente brevi da avere un impatto sul comparto automotive, è necessario valutare non solo la pianificazione, ma anche le...

-

onsemi presenta la piattaforma Treo

onsemi ha presentato Treo, una piattaforma analogica e a segnale misto realizzata nel nodo tecnologico avanzato da 65nm del processo BCD. Questa piattaforma fornisce le basi per una vasta gamma di soluzioni di onsemi per l’alimentazione e...

-

Gate driver ottimizzati per incrementare le prestazioni dei MOSFET SiC

Per far fronte alle esigenze del mercato, che richiede soluzioni caratterizzate da dimensioni sempre più compatte e alle pressioni esercitate sui progettisti per migliorare l’efficienza energetica, i MOSFET in carburo di silicio si stanno imponendo come una...

-

Uno sguardo al futuro della connettività alla periferia della rete nelle applicazioni industriali

La diffusione dell’automazione negli edifici e nelle fabbriche contribuisce a rendere il mondo odierno sempre più intelligente e connesso. Per garantire un funzionamento efficiente di questi nuovi sistemi è essenziale una comunicazione affidabile, a livello non solo...

-

I sistemi ADAS e di monitoraggio dell’abitacolo richiedono sensori di immagine protetti contro le minacce informatiche

La conformità alla cybersecurity è un requisito indispensabile per i sensori di immagine automobilistici, al fine di evitare che si trasformino in veri e propri ”cavalli di Troia” capaci di penetrare nei complessi sistemi elettronici di bordo...

-

Accordo pluriennale tra onsemi e Volkswagen

Il Gruppo Volkswagen ha scelto onsemi come fornitore di una soluzione completa di power box che farà parte dell’inverter di trazione di prossima generazione della sua Scalable Systems Platform (SSP). La soluzione power box di onsemi è...

-

La tecnologia elettronica al servizio della sostenibilità

Grazie all’adozione di soluzioni sostenibili è possibile ridurre sprechi, consumo di energia e gli oneri legati alla manutenzione Leggi l’articolo completo su EO519

-

onsemi investe in Repubblica Ceca per ampliare la produzione SiC

onsemi realizzerà in Repubblica Ceca un impianto per la produzione di componenti in carburo di silicio (SiC). Il sito produrrà i semiconduttori di potenza necessari per migliorare l’efficienza energetica delle applicazioni nei veicoli elettrici, nelle energie rinnovabili...

-

Migliorare la precisione dei circuiti elettronici di potenza mediante simulazioni accurate

Nel campo dell’elettronica di potenza e della simulazione circuitale, la precisione assume un’importanza fondamentale Leggi l’articolo completo su EO518