DIGITAL

ULTRA LOW POWER DESIGN

46

- ELETTRONICA OGGI 469 - APRILE 2018

I

nternet of Things (IoT) sta stimolando un’e-

norme richiesta di ogni genere di dispositivi

alimentati a batteria. A sua volta, questo crea

l’esigenza di un livello di efficienza energetica sem-

pre più elevato nei microcontrollori e in altri com-

ponenti a livello di sistema. Di conseguenza, ultra

low power (ULP) sta diventando la nuova formu-

la magica del marketing, specialmente quando si

tratta di descrivere i microcontrollori. Come primo

passo per comprendere il vero significato di ULP,

consideriamo le diverse implicazioni. In taluni casi,

quando la fonte di alimentazione è pesantemente

limitata (per esempio, nell’energy harvesting), si va

alla ricerca di correnti in modalità attiva più bas-

se possibili. In alternativa, quando il sistema passa la

maggior parte del tempo in modalità di standby o sleep

mode, con riattivazioni non frequenti (periodiche o asin-

crone) per l’elaborazione dei processi, si richiedono bas-

se correnti di sleep-mode. Inoltre, se la maggior parte del

lavoro viene svolta in un limitato periodo di tempo, l’ULP

può anche coinvolgere questioni di efficienza energetica.

In generale, un dispositivo alimentato a batteria utilizzerà

una combinazione di questi requisiti, basata su una serie

di compromessi. Naturalmente, l’ULP dipende anche da

opinioni e funzionalità – ad esempio, possiamo general-

mente considerare un’unità a micro controllore (MCU)

come ULP con la modalità attiva nell’intervallo tra 30 µA/

MHz e 40 µA/MHz e una corrente di shutdown da 50 nA a

70 nA. Tuttavia, la classificazione di un microcontrollore

come ultra low power dipende da una complessa combi-

nazione di caratteristiche che comprendono architettu-

ra, progetto del SoC, tecnologia di processo, periferiche

smart, e modalità deep-sleep. Nell’articolo saranno esa-

minati due microcontrollori da Analog Devices per aiuta-

re a comprendere come interpretare il vero significato di

ultra low power in questo contesto. Il meccanismo di cer-

tificazione del Consorzio EEMBC, che garantisce la veri-

dicità del punteggio relativo alla misura di potenza, ha lo

scopo di aiutare gli sviluppatori di sistema nella scelta

dei microcontrollori più appropriati alle loro soluzioni.

Misura e ottimizzazione dell’ultra low power

Per cominciare a comprendere l’ULP è utile spiegare la

modalità di misura. Di solito gli sviluppatori consultano

un data sheet, sul quale si trovano i valori di corrente

per MHz, e per le diverse modalità di sleep. Il primo pro-

blema che si pone, analizzando i consumi di corrente in

modalità attiva, è che il data sheet di solito non chiarisce

le condizioni nelle quali questi valori sono stati ottenu-

ti, ovvero quelle relative a codice, tensione e “wait state”

sulla memoria flash. Alcuni produttori usano un active

mode di riferimento, come il CoreMark EEMBC, mentre

altri ricorrono a sistemi più semplici come far girare uno

statement “while 1”. Se vi sono wait state sulla flash, a

causa dell’aumento dei tempi di esecuzione le presta-

zioni dell’unità microcontrollore risultano penalizzate,

aumentando, di conseguenza, i consumi energetici per

l’esecuzione di un task. Alcuni produttori forniscono

i dati di assorbimento ad una tensione tipica, altri alla

tensione minima, mentre altri non li specificano affatto.

Scelta del microcontrollore

per progetti ULP

Monica Redon

System Engineer – CSPT

(Consumer Sensing and Processing Technology)

Analog Devices

Il meccanismo di certificazione del Consorzio EEMBC, che garantisce

la veridicità del punteggio relativo alla misura di potenza, ha lo scopo

di aiutare gli sviluppatori di sistema nella scelta dei microcontrollori

più appropriati alle loro soluzioni

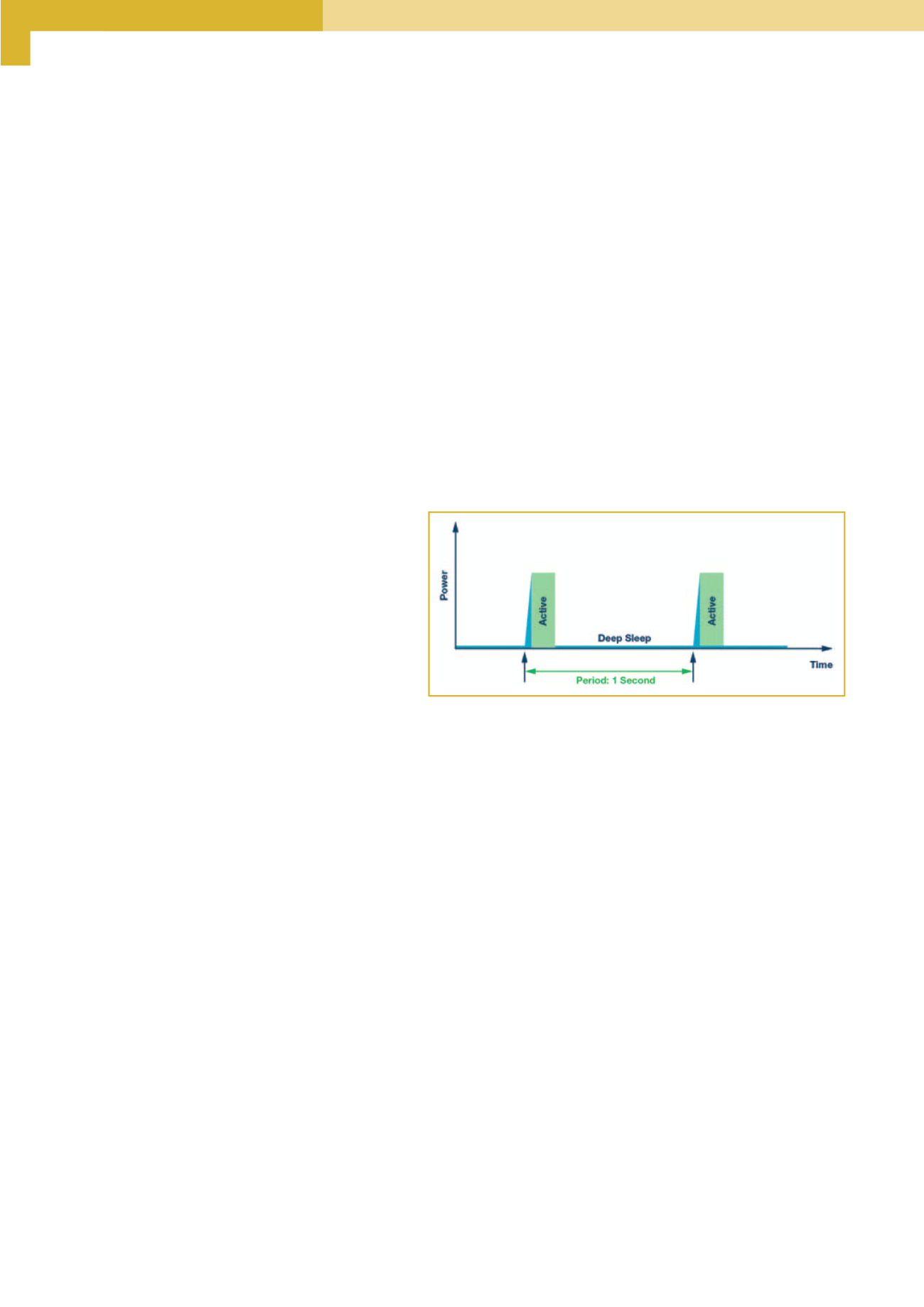

Fig.1 – L’ULPMark-CP ha un duty cycle di 1 secondo. Durante questo periodo, il

dispositivo si riattiva dal deep-sleep mode, esegue un test predefinito e ritorna

in deep-sleep