DIGITAL

ULTRA LOW POWER DESIGN

47

- ELETTRONICA OGGI 469 - APRILE 2018

Forse si tratta di differenze sottili

ma, in assenza di uno standard, i

confronti non possono che essere

approssimativi. In genere, sui data

sheet le modalità di deep-sleep

sono spiegate sufficientemente

bene ma, ancora una volta, gli assorbimenti di corrente

in queste modalità variano da un produttore all’altro (per

esempio, la quantità di memoria o la tensione utilizzate).

Inoltre, in un’applicazione reale, l’utente deve anche te-

ner conto dell’energia consumata nelle fasi di ingres-

so e uscita dalle stesse modalità. Questa può essere di

valore insignificante oppure molto rilevante, a seconda

se il dispositivo trascorre la maggior parte del tempo

in modalità sleep o viene riattivato di frequente. Questo

porta al punto successivo – ovvero il tempo trascorso da

un dispositivo in modalità sleep L’equilibrio tra gli stati

active e sleep è molto importante nella misura dell’ULP.

Per semplificare i processi, EEMBC utilizza il periodo

di un 1 secondo per il proprio ULPMark-CoreProfile

(ULPMark-CP), un benchmark utilizzato come standard

sui data sheet da molti produttori di microcontrollori.

Prendendo in considerazione il periodo attivo di lavoro

dell’ULPMark-CoreProfile, il duty cycle risulta intorno al

98%. In questo benchmark, il dispositivo viene attivato

una volta al secondo, svolge una piccola quantità di lavo-

ro (il ciclo attivo), quindi torna nello stato di sleep (Fig. 1).

Di solito, nell’active mode vi è una differenza nell’assorbi-

mento di corrente dovuta ai circuiti analogici e, pertanto,

minimizzare la corrente in modalità attiva e utilizzare in

modo appropriato il deep-sleep ha un impatto positivo

sull’ottimizzazione dell’uso delle energie di sistema. Si

noti che riducendo la frequenza, la corrente in modalità

attiva verrà ridotta a sua volta, ma il tempo di esecuzione

sarà incrementato, e la differenza di assorbimento dovu-

ta al circuito analogico, citato in precedenza, resta co-

stante mentre il microcontrollore è attivo. Tuttavia, quali

sono i compromessi nella scelta del microcontrollore, e

qual è l’impatto del duty cycle dell’applicazione e delle

correnti di deep-sleep sugli assorbimenti energetici? L’e-

nergia per ciclo, come funzione del duty cycle D (espres-

sa come percentuale del tempo di sleep mode rispetto

al tempo complessivo), è definita da un’equazione sem-

plificata che parte dal presupposto che le energie nelle

transizioni on e off siano di modesta entità.

dove la pendenza è definita da ION dato che ISLEEP è

molto inferiore a ION e l’intercetta di y è proprio ISLE-

EP. Quest’equazione può aiutare nella comprensione del

duty cycle nel quale la corrente in modalità attiva è più

importante di quella di sleep.

Le piattaforme di test ultra low power

Come si è detto precedentemente, ci si appresta al

confronto delle caratteristiche energetiche ultra low

power di due microcontrollori di Analog Devices—per

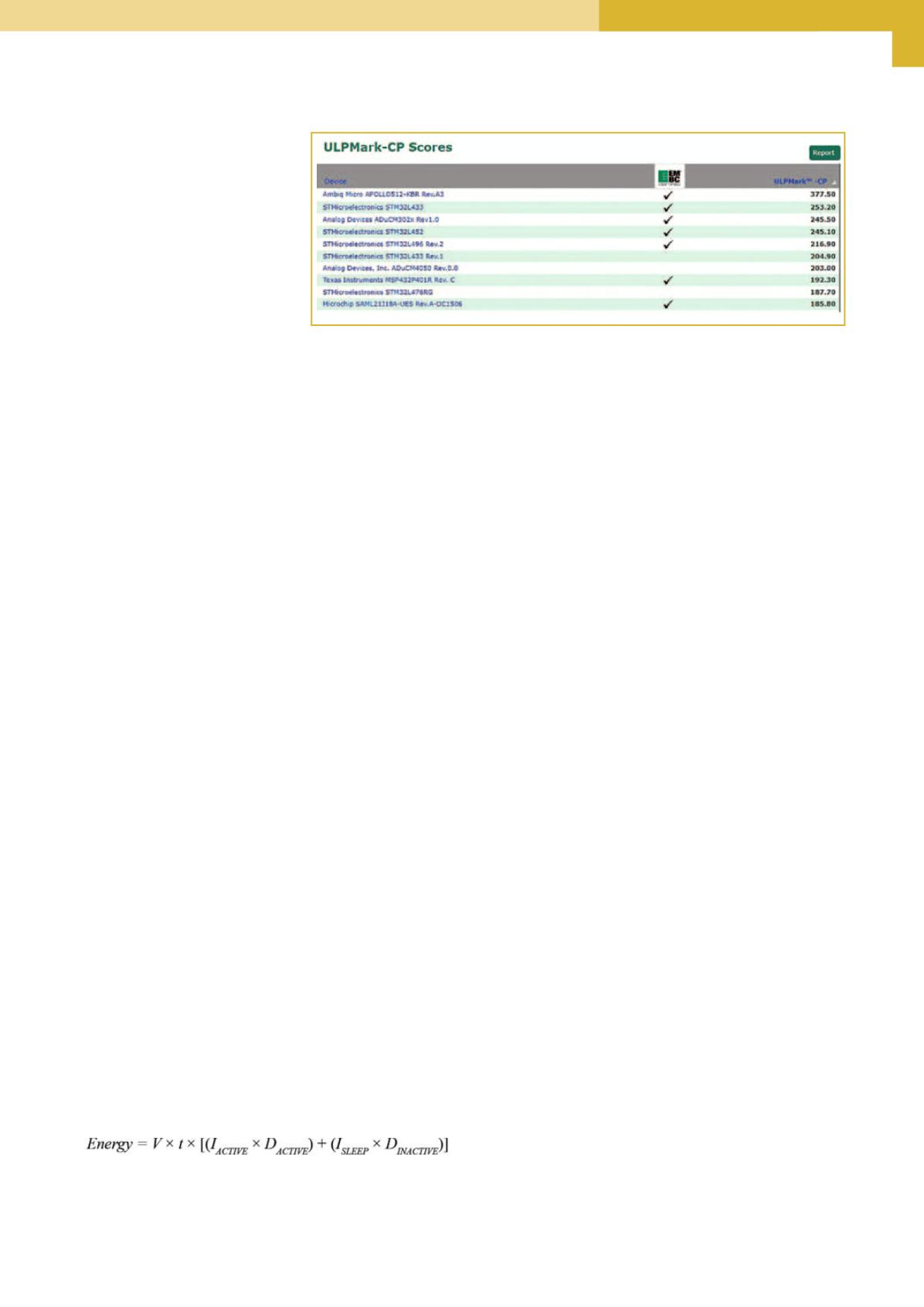

l’esattezza ADuCM4050 e ADuCM302x. Nella tabella

ULPMark (Fig. 2) ADuCM4050 e ADuCM302x raggiun-

gono il punteggio rispettivo di 203 e 245,5. È neces-

sario tenere presente che questo benchmark esegue

il test del core del microcontrollore (da cui il nome

CoreProfile). Da dove viene la differenza del 18%?

ADuCM4050 contiene un ARM Cortex-M4F che imple-

menta l’architettura ARMv7E-M e ADuCM302x contie-

ne un ARM Cortex-M3 che implementa l’architettura

ARMv7-M. Mentre entrambi i core hanno una pipeline

a 3-stadi ad esecuzione speculativa e sono entrambi

simili nell’architettura del set di istruzioni, solamen-

te il Cortex-M4F supporta istruzioni a virgola mobile

e DSP. Dal momento che non esistono istruzioni DSP

sull’ULPMark-CoreProfile, il Cortex-M4F non ricava al-

cun vantaggio dalla FPU.

Per le analisi di benchmark, l’ADuCM4050 e l’A-

DuCM302x sono stati utilizzati rispettivamente a 52MHz

e 26 MHz. L’ADuCM4050 richiede circa 11.284 cicli per

eseguire l’ULPMark, mentre l’ADuCM302x ne utilizza

10.920, il che permette al primo di completare la parte

in active mode in 217 µs del periodo disponibile di 1s,

mentre il secondo resta attivo per 420 µs. Il motivo per

cui l’ADuCM4050 utilizza qualche ciclo in più rispet-

to all’ADuCM3029 si spiega con le frequenze utilizzate

(52 MHz e 26 MHz, rispettivamente), l’ADuCM4050 ri-

chiede un wait state per la memoria flash, mentre l’A-

DuCM3029 non ne utilizza. Dato che l’ADuCM4050 è

dotato di memoria cache, aggiungendo un wait state

sulla flash non si hanno grosse penalizzazioni, visto

che molte delle istruzioni sono eseguite dalla stessa

cache memory, alla quale si può accedere a piena

velocità (52 MHz) senza bisogno di wait state supple-

mentari. Per quanto riguarda il tempo di esecuzione,

come ci aspettavamo, l’ADuCM4050 esegue il test più

velocemente dell’ADuCM3029, funzionando a una fre-

quenza pressoché doppia rispetto a quest’ultimo.

Fig. 2 – I primi 10 risultati

dell’ULPMark-CP, visibili

sul sito Web di EEMBC

(18 agosto 2017)

1