TECH INSIGHT

VISIONE ARTIFICIALE

18

- ELETTRONICA OGGI 465 - OTTOBRE 2017

intensiva. Uno dei requisiti più importanti in tale sistema è la sincronizzazione delle due catene di elaborazione

delle immagini. Quando si eseguono in parallelo le catene all’interno della matrice logica programmabile, questo

requisito può essere soddisfatto applicando lo stesso clock a ciascuna catena, soggetto a opportuni vincoli.

L’architettura dell’approccio omogeneo (Fig. 2) mostra le due catene di elaborazione delle immagini, che sono

basate prevalentemente su blocchi IP disponibili. I dati di immagine sono catturati usando un opportuno modulo

IP sensore-interfaccia e sono convertiti dal formato parallelo in flussi AXI. Ciò consente di ottenere una catena

di elaborazione delle immagini facilmente estensibile, i cui risultati possono essere trasferiti nella memoria DDR

del PS usando l’interconnessione AXI ad alte prestazioni combinata con video DMA.

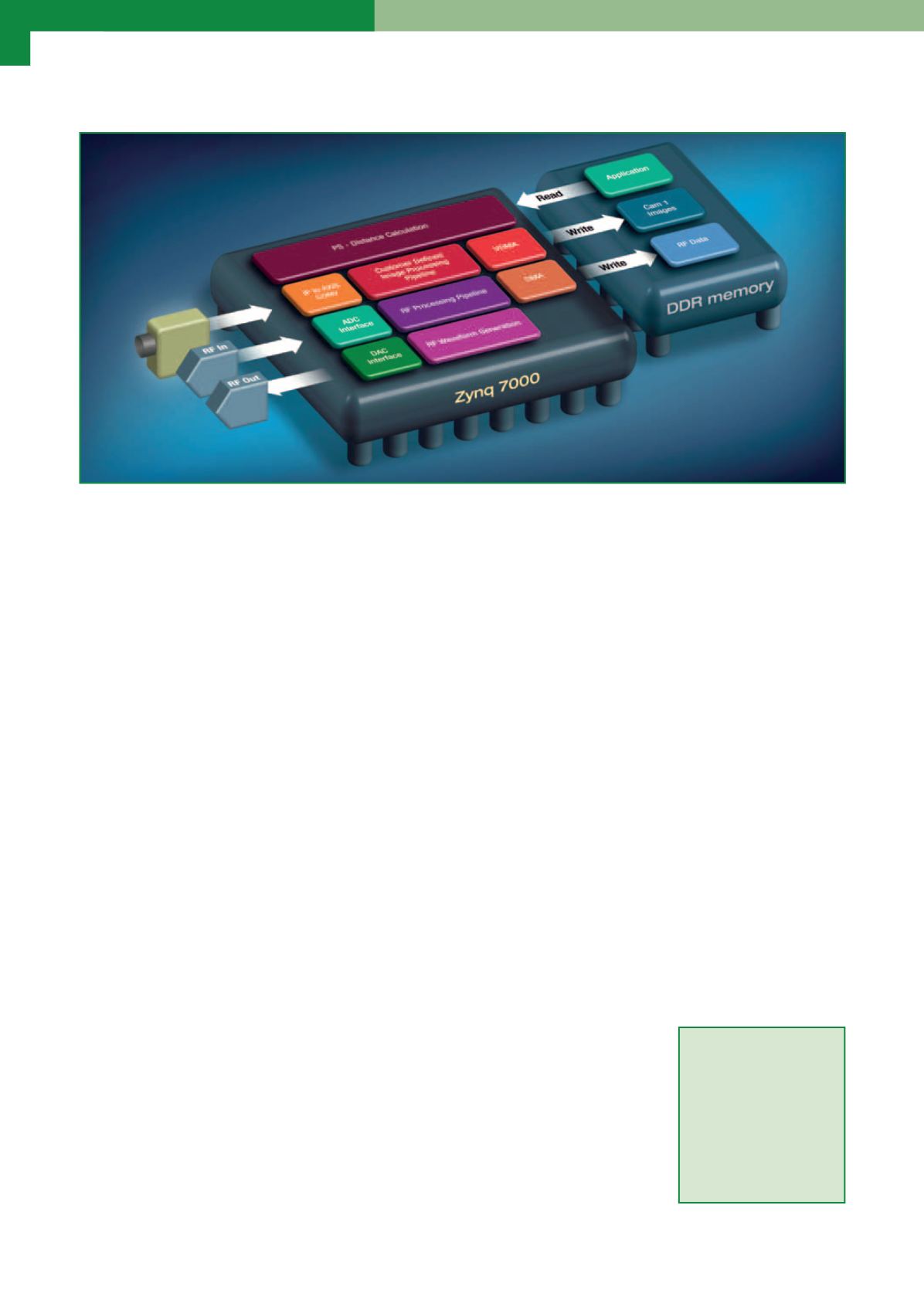

Se si considera un’implementazione che fa uso di diversi tipi di sensori, questa potrebbe combinare l’architettu-

ra di rivelazione degli oggetti descritta in precedenza con un RADAR per effettuare la rilevazione delle distanze.

Esistono due opzioni per implementare il RADAR: un approccio impulsato (Doppler) o ad onda continua. L’op-

zione migliore dipenderà dai requisiti dell’applicazione finale; tuttavia, entrambi seguiranno un approccio simile.

L’implementazione del RADAR (Fig. 3) può essere considerata come suddivisa in due parti: la generazione del

segnale che include un convertitore digitale-analogico ad alta velocità per produrre un’onda continua o un

segnale impulsato, e la ricezione del segnale usando un convertitore analogico-digitale ad alta velocità per

catturare il segnale ricevuto a onda continua o impulsato. Qualora occorra effettuare l’elaborazione dei segnali,

entrambi gli approcci ricorreranno all’analisi basata su FFT implementata con la matrice logica programmabile;

gli insiemi dei dati risultanti possono essere trasferiti alla memoria DDR del PS usando un DMA.

Per entrambe le implementazioni, l’algoritmo di fusione per entrambi gli insiemi di dati è effettuato con il PS

usando il software. Vale la pena osservare che i progettisti spesso osservano che gli algoritmi di fusione im-

pongono requisiti intensivi di banda di elaborazione. Un’opzione disponibile per ottenere prestazioni superiori

consiste nell’utilizzare la potenza dell’ambiente di progettazione SDSoC.

SDSoC consente di trasferire senza problemi le funzioni software fra il processore e la logica programmabile di

un SoC, usando Vivado HLS e un’infrastruttura per la connettività. Entrambi sono trasparenti allo sviluppatore

software. L’uso dell’HLS per sviluppare le catene di elaborazione sia nell’implementazione omogenea, sia in

quella eterogenea può essere ulteriormente esteso al fine di creare una piattaforma

SDSoC su misura per la realizzazione prescelta per gestire le risorse logiche non impe-

gnate, allo scopo di accelerare ulteriormente le prestazioni del sistema di visione em-

bedded nel complesso. Poiché i mercati dei sistemi di visione embedded continuano a

crescere, e i sensori di rilevazione delle immagini e altri tipi di sensore diventano più

prontamente disponibili e convenienti, i progettisti di sistemi necessitano di metodo-

logie di fusione sempre più veloci ed efficienti. Gli FPGA e i SoC interamente program-

mabili sono in grado di semplificare le catene di elaborazione multicanale, mentre

i tool di sintesi di sistema e ad alto livello contribuiscono ad assicurare prestazioni

superiori a livello di sistema e il completamento del progetto nei tempi prestabiliti.

Ulteriori

informa-

zioni sono reperibili

all’indirizzo:

http://

www. x i l i nx . com/

products/design-

tools/embedded-vi-

sion-zone.html

Fig. 3 – Fusione eterogenea dei sensori