DIGITAL

IC RAD HARD

43

- ELETTRONICA OGGI 463 - GIUGNO/LUGLIO 2017

gies. Si tratta di una tecnologia appositamente concepita

per consentire ai semiconduttori CMOS di resistere agli

effetti delle radiazioni. Ciascun dispositivo CMOS, indi-

pendentemente dalla geometria e dalla fabbrica in cui

è stato realizzato, può essere modificato con il processo

HARDSIL per renderlo immune da qualsiasi fenomeno

di latch-up. In funzione dello specifico processo, viene

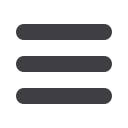

dispositivo. Questi fenomeni SEU possono influenzare

le celle di memoria o i circuiti logici. Un’altra caratte-

ristica dell’architettura del microcontrollore VA10820 è

l’implementazione della ridondanza tripla (TMR – Triple

Modular Redundancy) su tutti i registri interni. Mentre il

sistema EDAC si occupa delle problematiche SEU all’in-

terno della memoria, il TMR affronta le medesime pro-

blematiche nei circuiti logici. Nella figura 2 è riportato

lo schema a blocchi del microcontrollore VA10820. I bit

della memoria EDAC sono fisicamente collocati nella

stessa matrice (array) delle parole di memoria. Durante

la sequenza di accensione (power-on) del microcontrol-

lore VA10820 l’intero spazio di memoria è inizializzato in

uno stato noto in modo tale che ciascun indirizzo inizi

con uno stato valido (clean state). Poiché ci sono 5 bit

EDAC per ogni byte nella parola di dati a 32 bit interna, è

possibile rilevare 2 errori sui singoli bit per ogni lettura

di byte e correggere 1 bit per ogni byte della parola di

memoria a 32 bit. Ciò consente la correzione di un mas-

simo di 4 errori sui bit (1 per byte) per parole di dati a 32

bit. La decisione di utilizzare 5 bit di parità per ogni byte

di memoria è stata dettata da due ragioni. La prima è la

garanzia del supporto della scrittura a byte (byte write)

tipica dei moderni microcontrollori e la seconda è che

rappresenta un compromesso ottimale tra la dimensio-

ne della matrice di memoria e la velocità di accesso in

lettura/scrittura da/verso la memoria interna.

Tecnologia CMOS resistente alle radiazioni

I chip utilizzati in questa applicazione sulla Stazione

Spaziale Internazionale sono stati realizzati utilizzando

il processo HARDSIL sviluppato da VORAGO Technolo-

Fig. 2 – Schema a blocchi della MCU VA10820 resistente alle radiazioni sviluppata da VORAGO Technologies