COMM

RETI PON

62

- ELETTRONICA OGGI 457 - OTTOBRE 2016

zati a velocità doppia e il serializzatore in trasmissione

genera sempre due bit identici per ciascun bit diretto

verso la CO. In questo modo, a livello di struttura, la

piattaforma hardware può emulare un salto di 0,5 in-

tervalli unitari fra due pacchetti consecutivi – il caso

peggiore in un ambiente PON. Una piattaforma har-

dware sollecita il BCDR, inserendo una fase che simula

il caso peggiore fra ciascuna coppia di

pacchetti.

Il carico utile in questa piattaforma è

una sequenza PRBS troncata, che si

riavvia dopo il delimitatore in ciascun

pacchetto. Se il BCDR salta un pac-

chetto, si osserverà un errore nel ca-

rico utile.

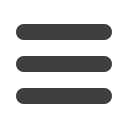

È anche prevista la possibilità di mo-

dificare la lunghezza del preambolo in

corso d’opera. Il banco di prova com-

pleto è definibile attraverso script, e

Vivado Hardware Analyzer è incluso in

questo testbench assieme a numerosi

controlli, come mostrato in figura 6.

Oltre al test hammer, all’inserimento

degli errori e all’accumulo, è possibi-

le modificare in corso d’opera le nu-

merose caratteristiche del SerDes e

molte funzionalità del BCDR – come la

sua banda digitale. La configurazione

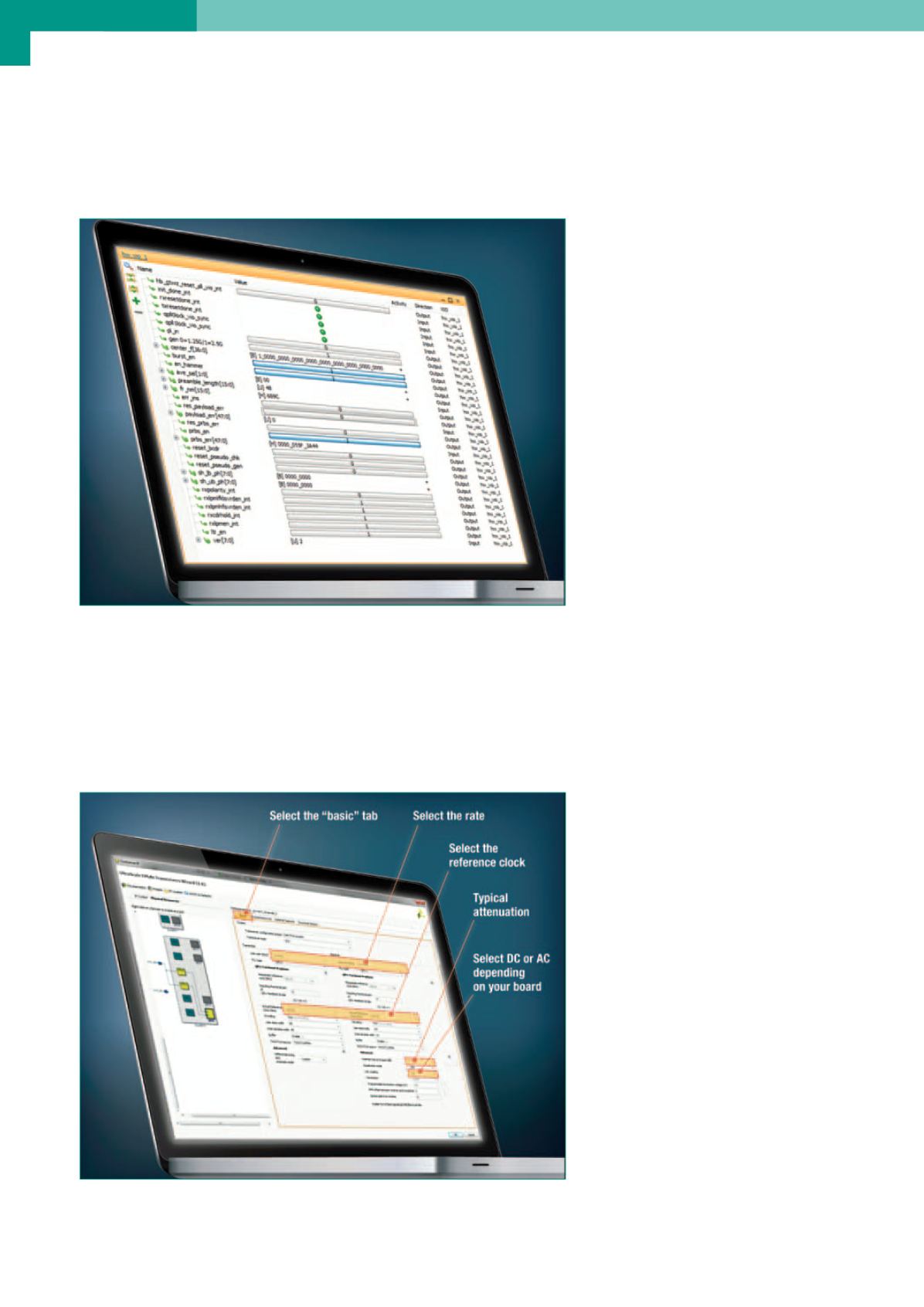

del SerDes costituisce un altro aspetto

che talvolta preoccupa gli utenti che non hanno gran-

de familiarità con la tecnologia FPGA, perciò la piatta-

forma BCDR include istruzioni con descrizioni passo-

passo per la configurazione del SerDes, per aiutare

l’utente a impostare un’interfaccia in un’unità OLT di

una PON. La figura 7 mostra come la piattaforma guida

l’interfaccia GUI Wizard del Gigabit Transceiver (GT) e

cela la complessità dell’hardware.

Queste tecniche consentono di sele-

zionare un prodotto complesso come

un BCDR usando semplicemente

una GUI. Una volta valutato il BCDR,

il banco di prova dell’hardware è il

miglior punto di partenza per il pro-

getto reale. È possibile includere il

BCDR semplicemente rimuovendo il

generatore/controllore del pacchetto

demo e sostituendo tali moduli con

un MAC PON reale.

La famiglia UltraScale di Xilinx è at-

tualmente in produzione. I BCDR da

1,25Gbps e da 2,5Gbps sono dispo-

nibili attraverso XAPP1277. Con la già

citata IP per reti PON e il gran numero

di dispositivi UltraScale interamente

programmabili già in produzione, Xi-

linx offre la piattaforma ideale e più

scalabile per progettare gli apparec-

chi OLT di prossima generazione.

Fig. 6 – Vivado Hardware Analyzer all’interno del banco di prova hardware

Fig. 7 – La configurazione del SerDes per l’impostazione di un’interfaccia OLT a più velocità