JTAG/BOUNDARY SCAN

62

- ELETTRONICA OGGI 454 - MAGGIO 2015

EDA/SW/T&M

mostrano come i test point inutilizzati possono incrementare

in maniera significativa la copertura del test (test coverage).

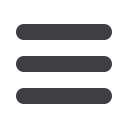

Come primo esempio, la figura 6 mostra una banco di RAM il

cui clock viene distribuito da un PLL. Un accesso statico a tutti

i pin IC è necessario per verificare i componenti di RAM con il

Boundary Scan. Questo però non è possibile per il segnale di

clock: ciò genera un’importante abbassamento della test co-

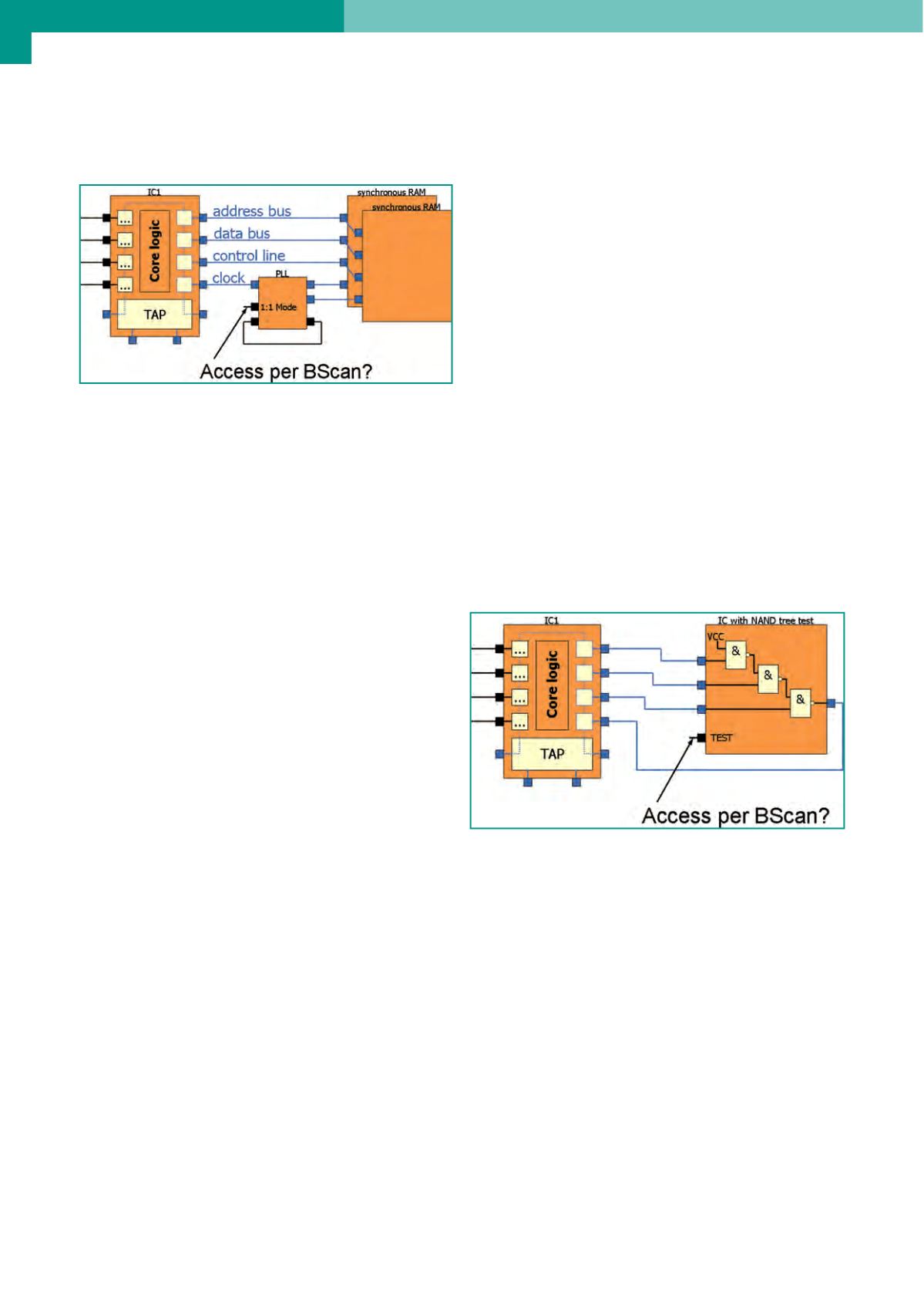

verage.Lafigura 7 mostra quanto decisivo sia l’accesso a un

unico pin IC per poter testare completamente un componente.

L’immagine mostra un componente NAND da testare. Potreb-

be essere testato in Boundary Scan, a condizione che le NAND

possano essere attivate da un pin specifico (nell’immagine 7 è

chiamato “TEST”).

Standard futuri

Il successo dello standard IEEE1149.1 di JTAG / Boundary

Scan ha ispirato e incoraggiato tutti gli operatori del settore a

migliorare questa tecnologia di test, rendendola il più possi-

bile svincolata da limitazioni. Tra i numerosi standard parzial-

mente istituiti segnaliamo i seguenti:

IEEE1149.4

L’affermarsi di tale standard potrebbe forse significare la

fine del classico test In Circuit, perché l’IEEE1149.4 è un

test a “mixed signal” o anche di interconnessione analogica.

Il metodo è molto semplice. Oltre ai quattro/cinque (op-

zionale) segnali, due nuovi segnali analogici ATAP ven-

gono aggiunti: “Analogue Test 1 (AT1)” e “Analogue Test

2 (AT2) “. Questi pin possono essere commutati inter-

namente indipendentemente uno dall’altro nel caso di

componenti compatibili con standard IEEE Std. 1149.4.

SipotrebbedirecheuncomponenteIEEE1149.4haunamatricedi

relèinterna,chepuòesserecommutataaognipintramitetestbus.

Cercare di raggiungere con opportuni limiti le potenzialità del

test In-Circuit è possibile connettendo verso l’esterno l’ATAP.

IEEE1149.6

Lo standard IEEE1149.6 permette di testare connessioni se-

riali ad alta velocità. Esso descrive il test di interconnessione

“Advanced Digital Network”.

La possibilità di lavorare con i segnali TAP esistenti è il suo

più grande vantaggio. La norma richiede un paio di istruzio-

ni in più, una cella Boundary Scan leggermente modificata e

un generatore di test pattern integrato. Il principio di nuovo è

molto semplice. Alcuni pin IEEE Std. 1149.6 sono connessi a un

nuovo tipo di celle Boundary Scan. In contrasto con i “vecchi”

tipi di celle, queste hanno un ingresso speciale, che è collegato

al generatore di test pattern integrato.

Per ogni istruzione, queste celle Boundary Scan passano al

nuovo input e il generatore di test pattern manda il test pat-

tern alla cella Boundary Scan, quindi al pin, indipenden-

temente dal segnale “Test Clock”. Ciò è valido per l’invio.

Allo stesso tempo sul lato recezione, il test pattern viene letto

e scritto in un buffer. In seguito a ciò, il test pattern ricevuto

viene verificato generando così un Pass / Fail. Questa risultato

è allocato in una cella Boundary Scan come 0 o 1, e può essere

letto e valutato dal sistema di test.

JTAG / Boundary Scan è la tecnologia di test senza dub-

bio più geniale sul mercato. Rappresenta il salto dall’ac-

cesso fisico alle piste di una scheda con tutte le sue limita-

zioni, a un accesso di tipo elettrico e illimitato. La tecnologia

JTAG / Boundary Scan richiede solo quattro linee di con-

trollo e una manciata di regole per la Design for Testability.

Quando si parla di JTAG o Boundary Scan, ci si riferisce alla

IEEE Std. 1149.1 – e cioè a un tipo di test di interconnessione

digitale e statico.

Le sole limitazioni di questa tecnologia riguardano gli

aspetti analogici e quelli dell’alta velocità. Ma le soluzio-

ni apportate dalle IEEE 1.149,4 e 11.149,6 hanno esteso

l’utilizzo di JTAG / Boundary Scan anche per tali aspetti.

Uno sviluppatore di test Boundary Scan non deve avere a che

fare con ogni dettaglio tecnologico poiché gli strumenti mo-

derni basati su modelli dei componenti, eseguono la maggior

parte dell’attività di test.

Fig. 7 – Accesso completo

Fig. 6 – Banco di RAM con PLL