JTAG/BOUNDARY SCAN

60

- ELETTRONICA OGGI 454 - MAGGIO 2015

EDA/SW/T&M

nente dalla catena. La sua lunghezza minima è solo di un bit e

non può essere modificato. Il registro “boundary-scan” defini-

sce la successione delle singole celle Boundary. Poiché ogni

chip ha un numero diverso di Celle boundary scan, la lunghez-

za del registro è variabile.

Le celle Boundary Scan

La cella Boundary Scan è l’elemento essenziale della metodo-

logia di Test Boundary Scan.

Tutte le funzioni descritte fin qui sono costituite per il corretto

controllo delle rispettive celle di Boundary Scan.

La cella Boundary Scan dà la possibilità di controllare un pin

di un componente disconnettendolo dalla sua funzionalità nor-

male ad esempio per pilotare o misurare un livello logico. Per

tale scopo la cella Boundary Scan è situata tra la logica di base

del componente e una periferica (output driver, input driver).

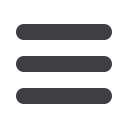

La funzionalità è simile a quella degli aghi fisici utilizzati nei

test In-Circuit, che si connettono ai test point della scheda; per

questo motivo le celle Boundary Scan sono anche chiamate

“aghi elettronici” (si faccia riferimento alla Fig. 3).

L’architettura interna di una cella Boundary Scan può essere

molto variabile. A partire dal 2001, la IEEE Std. 1149.1 descri-

ve dieci diversi tipi di celle (dalla BC_1 alla BC_10). La cella

può avere una sua struttura per quanto la loro disposizione sia

spesso molto simile.

Boundary Scan Description Language (BSDL)

Ogni componente ha una struttura Boundary da tener pre-

sente affinché i test possano essere efficacemente svolti. Lo

standard IEEE 1149.1 detta i requisiti di base inderogabili,

ma lascia spazio per sviluppi in autonomia. Questo è neces-

sario, come si vedrà per esempio riguardo la struttura / nu-

mero di celle Boundary Scan: un circuito integrato con 20

pin ha un minor numero di celle rispetto a uno con 1.500 pin.

Il “Boundary Scan Description Language (BSDL)” è stato svi-

luppato per definire la sua struttura JTAG. È la piattaforma di

scambio tra i produttori di chip (solo loro conoscono la struttu-

ra interna dei propri chip) e gli ingegneri di test (che vogliono

poter utilizzare tale struttura interna). Il BSDL è un file di dati

che fornisce le specifiche per:

•

Caratteristiche dei segnali di test (in particolare le infor-

mazioni circa l’esistenza del segnale opzionale / TRST e la

frequenza massima TCK, alla quale il componente può ope-

rare)

•

Possibili pin “compliance”

•

Instruction register (istruzioni disponibili incluso il bit code

e la sua lunghezza)

•

Data register (disponibilità registro dati con inclusi i valori

predefiniti, quali l’IDCODE)

•

Struttura della cella Boundary Scan (numero, tipo, funzione,

collegamento a pin fisico)

Vantaggi e limiti della IEEE Std. 1149.1

Il test di interconnessioni digitali secondo la IEEE Std. 1149.1

abilita tutto ciò che si trova nella sfera digitale e non è fun-

zione del tempo. Così, è possibile testare la presenza di resi-

stenze, quarzi, driver, porte logiche, reset e persino RAM o

Flash (sia parallele sia seriali). Si tratta quindi dello stesso ap-

proccio del test funzionale limitato in frequenza dalla catena

Boundary Scan. Per le Flash i protocolli necessari di Write e

Read sono emulati attraverso i pin Boundary Scan. Il limite di

tale tecnologia è proprio la massima frequenza del segnale sui

pin Boundary Scan (quindi la lunghezza del registro Boundar

Scan e il Test Clock “TCK”). Non importa se il livello del segnale

di uno o più pin deb-

ba cambiare – in ogni

caso esso deve passa-

re attraverso TUTTE le

celle (Scan Shift). Tale

processo di shift impie-

ga, in un componente

Boundary Scan di me-

die dimensioni con 500

celle e una frequenza

tipica di 10 MHz, 50 µs.

Tuttavia, un proces-

so di shift può avviare

una cambio di segnale

unico sul singolo pin.

Per il fronte opposto è

richiesto un altro shift che si traduce in una frequenza massi-

ma raggiungibile di 100 µs-1, quindi 10 kHz.

I vantaggi delle nuove soluzioni Boundary Scan

Attualmente vi sono alcuni requisiti di sistema di test Boundary

Scan. L’utente, ad esempio, non vuole preoccuparsi di lavora-

re sul corretto switching del segnale di TMS (Test Mode Select)

per accedere al corretto stato della macchina a stati Boundary

Scan. Al massimo gli interessa definire le modalità operative

per il test dei circuiti integrati. Fortunatamente gli strumenti

moderni permettono di semplificare questo lavoro. Che cosa

Fig. 3 – Confronto dei metodi di prova ICT e Boundary Scan

Fig. 4 –Hardware - Boundary Scan control-

ler di GOEPEL electronic (SFX-TSL1149.x)