JTAG/BOUNDARY SCAN

59

- ELETTRONICA OGGI 454 - MAGGIO 2015

EDA/SW/T&M

testing di grandi produttori di chip europei. Nel 1986, ulte-

riori aziende del Nord America hanno aderito all’iniziativa e

il gruppo è stato rinominato Joint Test Action Group” (JTAG).

JTAG sviluppò una metodologia simile al metodo LSSD svilup-

pato da Ed Eichelberger, definendo però in aggiunta elementi

di memoria all’interno di un chip che sono tra loro collega-

ti in catena. L’unica differenza è che gli elementi di memoria

vengono allocati nella periferia, in inglese “at boundaries”

del componente. Ecco perchè tale metodologia fu chiamata

“Boundary Scan” e fu standardizzatata come 1149.1 “Standard

Test Access Port and Boundary Scan Architecture” dall’Insti-

tute of Electrical and Electronics Engineers (IEEE) nel 1990.

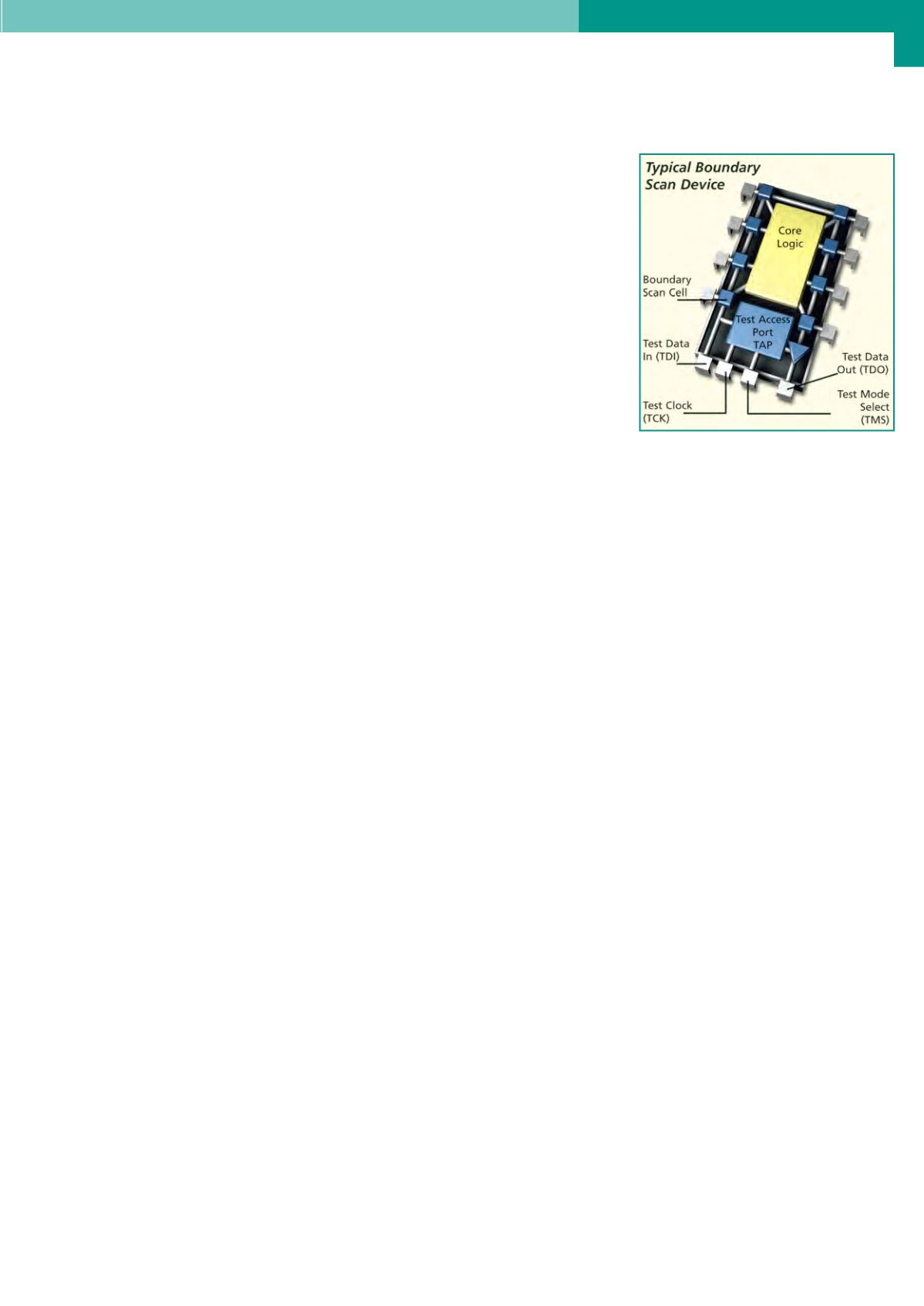

Lo standard Boundary Scan IEEE 1149.1

Lo standard Boundary Scan IEEE 1149.1 descrive il test sta-

tico per le interconnessioni digitali. Le sigle Boundary Scan

o JTAG sono sinonimi e indicano sempre lo standard IEEE

1149.1. Tale standard descrive sia l’architettura di un com-

ponente Boundary Scan sia il suo linguaggio descrittivo: il

“Boundary Scan Description Language (BSDL)”, che deli-

nea le risorse boundary scan uniche per ogni componente.

IEEE Std. 1149.1 definisce l’architettura interna di un chip

Boundary Scan, che consiste di quattro parti essenziali:

•

Un test Access Port (TAP)

•

Un Controller TAP

•

Una Registro di istruzioni (Instruction register)

•

Uno o più data register

Test Access Port (TAP)

Il “Test Access Port” è il componente Boundary Scan e dispo-

ne di tre ingressi (più un quarto opzionale) e un’uscita. Gli in-

gressi sono:

•

Test Clock (TCK)

•

Test Mode Select (TMS)

•

Test Data Input (TDI)

•

Test Reset (/ TRST) – opzionale

L’uscita è:

•

Test Data Output (TDO)

Un tipico circuito Boundary Scan è riportato in figura 2.

Entrambi i segnali TCK e TMS, nonché il segnale opzionale /

TRST sono segnali broadcast, mentre il TDI e il TDO, connes-

si in catena, costituiscono la catena JTAG: scan chain / path.

L’insieme di questi segnali è definito come “Test Bus”.

Non sono mai necessari più di quattro linee di segnali (cin-

que opzionali) – indipendentemente da quanti componenti

vengono collegati in catena. Nel chip Boundary Scan, il Test

Clock, il Test Mode Select come anche il Test Reset sono di-

rettamente collegati (staticamente) con il TAP controller. Lo

stato del TAP Controller

è esclusivamente defini-

to da questi segnali. Ciò

significa che tutti i com-

ponenti Boundary Scan

nella catena di scansione

hanno lo stesso TAP state.

Ma ciò non significa che

tutti componenti devono

avere la stessa modalità di

funzionamento / istruzioni.

TAP controller

•

Il TAP controller è responsabile per l’intero controllo della

logica Boundary Scan nel chip, cioè è responsabile se una

cella Boundary Scan (si veda il capitolo Boundary Scan del-

le celle) è attivata o disattivata e se devemisurare o pilotare.

Nel cuore del TAP controller vi è la macchina a stati TAP.

I diversi stati della macchina controllano la logica interna

Boundary Scan.

Instruction Register

L’instruction register sceglie la modalità di funzionamento del

dispositivo Boundary Scan, che a sua volta controlla le celle

Boundary Scan nonché la selezione del data register selezio-

nato nella catena Boundary (registro tra TDI e TDO).

L’IEEE Std. 1149.1 definisce tre istruzioni mandatorie:

•

BYPASS

•

SAMPLE / PRELOAD

•

EXTEST

A ogni istruzione corrisponde un bit code. Esso può essere

liberamente definito da ciascun produttore di chip (l’unica ec-

cezione è l’istruzione BYPASS).

La lunghezza del registro di comando può essere definito ar-

bitrariamente. Un esempio è lo schema indicato nella tabella

1. La lunghezza del registro di istruzione è stata perciò definita

a due bit.

Data Register

Un componente Boundary Scan può contenere più data regi-

ster. Sono utilizzati per archiviare o trasmettere informazioni

nel componente. Lo standard IEEE Std 1149.1 definisce un mi-

nimo di due data register obbligatori:

•

Bypass

•

Boundary-scan

Registri aggiuntivi possono essere previsti, ad esempio il “de-

vice identification” o colloquialmente “IDCODE”.

Il registro “bypass” dà la possibilità di escludere un compo-

Fig. 2 – Esempio di un tipico circuito

Boundary Scan