JTAG/BOUNDARY SCAN

58

- ELETTRONICA OGGI 454 - MAGGIO 2015

EDA/SW/T&M

Tecnologia JTAG / Boundary

Scan: un’analisi

delle sue potenzialità

e delle modalità di utilizzo

S

in dalla nascita dei circuiti integrati vi è stata la necessità

di controllare le loro funzioni. In tale circostanza il test è

moltosemplice:tuttiipossibilivettoriditestsonoapplicati

in successione, e quindi le reazioni dei circuiti sulle uscite (valo-

re reale) sono confrontati con i modelli attesi (valore nomina-

le). Se non vi sono differenze il circuito funziona correttamente.

Il numero di vettori di test è gestibile con una semplice porta

AND a due ingressi. Secondo Moore e McCluskey il numero è

ottenibile dalla seguente formula:

Q=2(x+y)

Dove

Q = numero minimo di vettori di test

x = numero degli ingressi

y = numero di elementi di memoria (per circuiti sequenziali)

Poiché una porta AND normalmente non ha elementi di me-

moria, ci sono solo quattro vettori di test necessari – che è un

numero gestibile. Se questo calcolo è fatto per un circuito con,

per esempio, 25 ingressi e 50 elementi di memoria, i problemi

di sviluppo dei chip che gli ingegneri dovettero affrontare a

partire dal 1970 diventano evidenti.

All’inizio degli anni ‘70, IBM ha ideato una soluzione a tale

problema con l’invenzione del metodo “Level Sensitive Scan

Design (LSSD)” dove gli elementi di memoria di un chip esten-

dono le loro funzioni. Si aggiungono quindi quattro segnali: un

ingresso (IN), un’uscita (OUT) e due clock (A e B), come ripor-

tato in figura 1.

Con questa soluzione divenne quindi possibile acce-

dere agli ingressi e uscite degli elementi di memoria.

All’inizio del 1980, il problema della crescente complessità

dei PCB con maggiore densità di packaging fu nuovamente

affrontato. Il Joint European Test Action Group, fondato nel

1985, è stato uno dei primi istituti che ha affrontato questo

tema. Ai tempi, questo gruppo era composto da tecnici del

A cura di GOEPEL electronic

La tecnologia di test BoundaryScan/JTAG si

sta via via affermando quale indispensabile

risorsa presso gli specialisti del test. Qui

di seguito un chiarimento sul principio

di funzionamento, caratterizzazione dei

prerequisiti e dei vantaggi di tale tecnologia

e uno sguardo sui futuri sviluppi

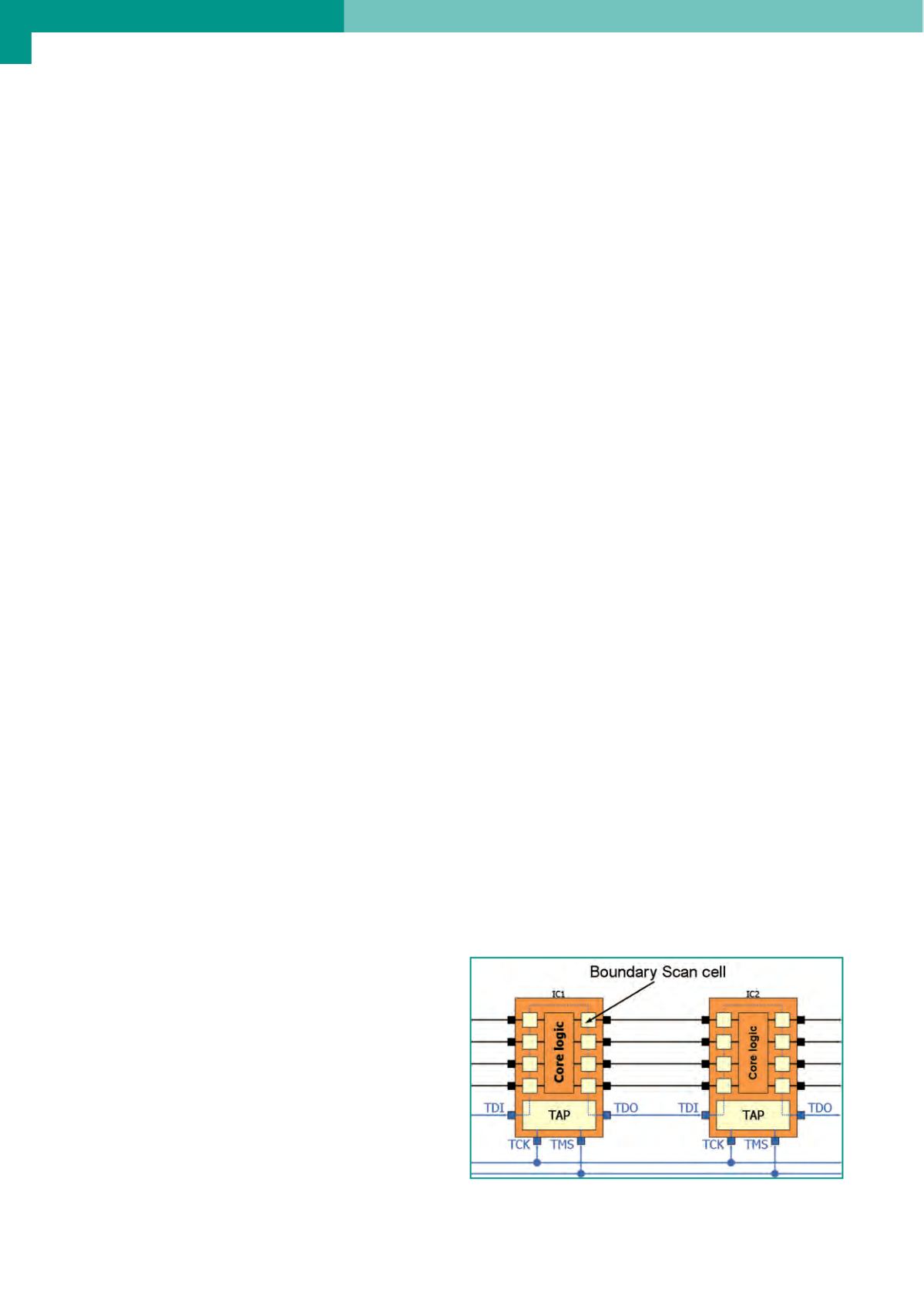

Fig. 1 – Collegamenti bus per due Boundary Scan Ics