JTAG/BOUNDARY SCAN

61

- ELETTRONICA OGGI 454 - MAGGIO 2015

EDA/SW/T&M

significa il termine Boundary Scan tool? Un si-

stema di test Boundary Scan (un esempio è ri-

portato in Fig. 4) consiste di una parte hardware

ed una software. La parte hardware deve “solo”

essere in grado di controllare i segnali TAP. Ogni

Hardware Boundary Scan ha tale funzionalità di

base (con differenze importanti in termini di pre-

stazioni, velocità effettiva e flessibilità).

I produttori di tecnologia Boundary Scan si dif-

ferenziano per quanto riguarda l’aspetto del

software, e questo è il motivo principale per cui,

quando si parla di strumenti Boundary Scan, si parla essen-

zialmente di software.

Da un moderno software Boundary Scan ci si aspetta che

generi automaticamente i necessari vettori di test e probabil-

mente che guidi velocemente l’operatore a diagnosticare il

fault sulla scheda sotto test.

Se è necessario integrare un test

Boundary Scan su una linea di

produzione lo strumento Bounda-

ry Scan deve poter permettere un

agile interfacciamento verso altre

macchine di test.

Design for Testability (DFT)

I migliori sistemi di test Boundary

Scan con i più potenti Test Program Generators (ATPG) sono

poco efficienti se non sono state osservate particolari regole

di progettazione durante lo sviluppo o addirittura in prece-

denza, durante la selezione dei componenti. Di seguito alcuni

criteri basilari per la testabilità di un prodotto, il più importan-

te è il Compliance Pattern.

Con l’utilizzo di componenti Boundary Scan, è normale con-

dividere la Tap con altre funzioni, come ad esempio il debug-

ging. Per questo motivo, tale componente di solito ha un pin

dedicato che ne determina la funzione. Questo pin potrebbe

essere chiamato ad esempio JTAG # / DEBUG, e potrebbe at-

tivare il debug mode del componente. In tale caso uno stato

basso deve essere applicato per poter testare con la meto-

dologia Boundary Scan: diversamente è negato l’accesso alle

risorse JTAG dello stesso.

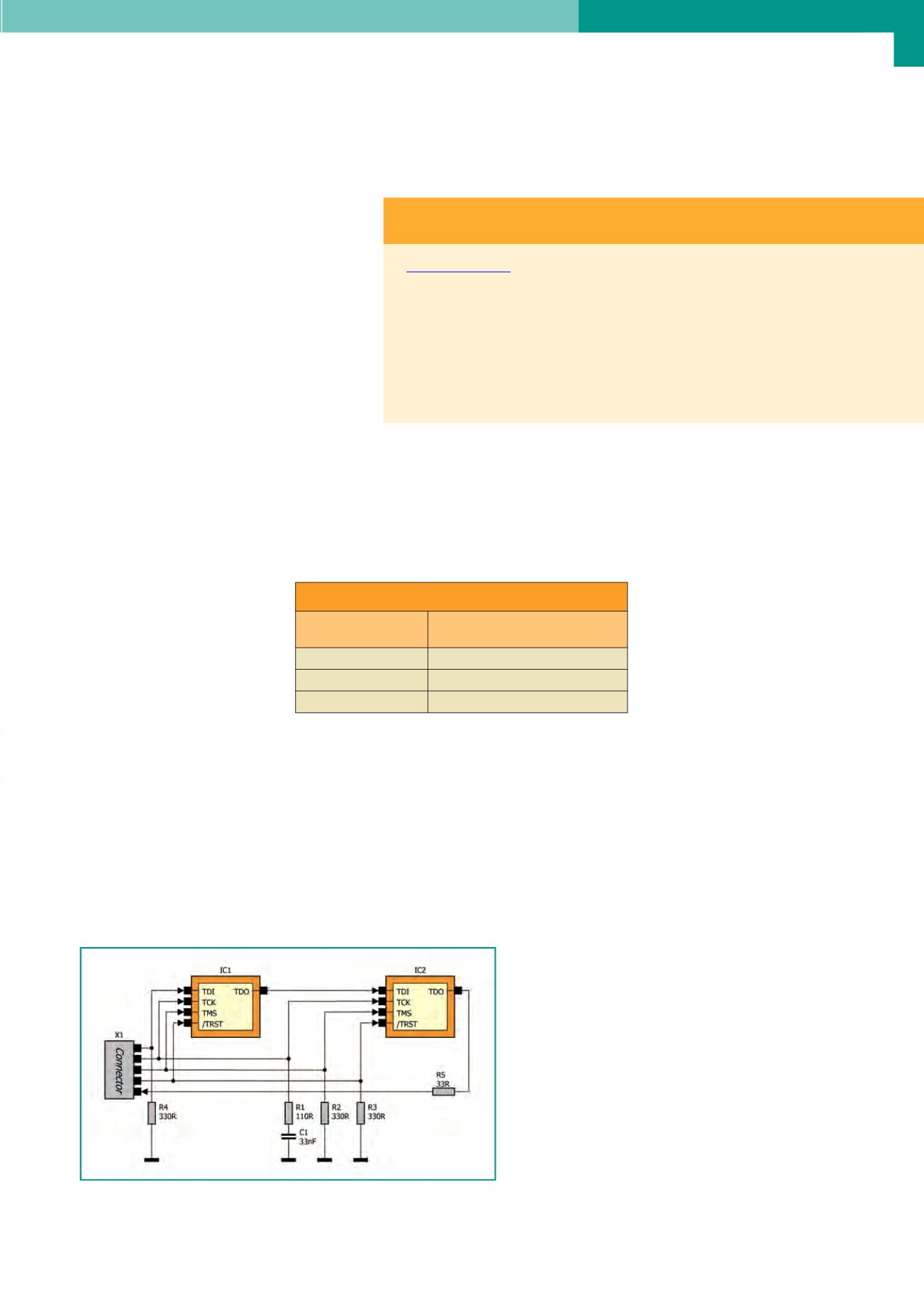

Terminazione del Bus di Test

La terminazione del bus di

test (Fig. 5) è essenziale per

l’esecuzione di un test veloce.

Come principio guida, il tempo di

test è proporzionale al TCK.

I più efficaci sistemi di test sono in

grado di elaborare il segnale TCK

a 80 o 100 MHz. È, in tal caso, fon-

damentale aver cura del cablaggio della TAP.

Flessibilità della catena Boundary

È pratica comune produrre schede in diverse varianti di mon-

taggio. Si consiglia cautela se tale variante di montaggio è su

componenti Boundary Scan. Può capitare infatti che un com-

ponente IC non sia presente in catena e di conseguenza il bus

di test (TDI

➞

TDO) risulti quindi interrotto. Il risultato sarebbe

un completo fallimento.

Accessibilità equivale a successo

Questa regola chiave per la Design Testability è valida

non solo per il classico test In-Circuit, ma anche per la

tecnologia Boundary Scan. Solo l’implementazione è

diversa nei due casi. Utilizzare il test in-circuit significa

impostare test point, ove possibile.

Al contrario, nel caso del test Boundary Scan tali test

point (o pin) risultano “dormienti” e parzialmente inutiliz-

zati nei componenti Boundary Scan come pin non con-

nessi.

Questo perché tali pin non sono necessari durante la

funzione “normale” della scheda. In tal caso si riducono i

test point reali, riducendo costi di sviluppo e produzione.

Nelle figure 6 e 7 sono riportati due esempi tipici che

G

Ö

EPEL

in pillole

GÖPEL Electronicsviluppa e produce soluzioni intelligenti per il test di schede e

di dispositivi elettronici. L’azienda è uno dei pionieri della più innovativa tecno-

logia di test JTAG / Boundary Scan. Tutte le attività di ingegnerizzazione neces-

sarie per introdurre la tecnologia Boundary Scan, la generazione di programmi

di test specifici per il prodotto, nonché i seminari di formazione sono parte del

sostegno globale al cliente che GOEPEL Electronic fornisce. Il test funzionale di

schede elettroniche e dispositivi, in particolare per il settore Automotive, è uno

dei pilastri di sostegno dell’attività di Göpel.

Tabella 1 - Esempio di un registro istruzione

Operation

mode/instruction

Instruction

code (binary)

BYPASS

11

SAMPLE/PRELOAD

01

EXTEST

00

Fig. 5 – Terminazione del bus di test